锤子

集成电路(IC)封装的界面显微组织检验方法

- 类别:分析方法/应用文章

- 上传人:标乐

- 上传时间:2006/10/20 1:30:30

- 文件大小:1842K

- 下载次数:537

-

消耗积分 : 免积分

简介:

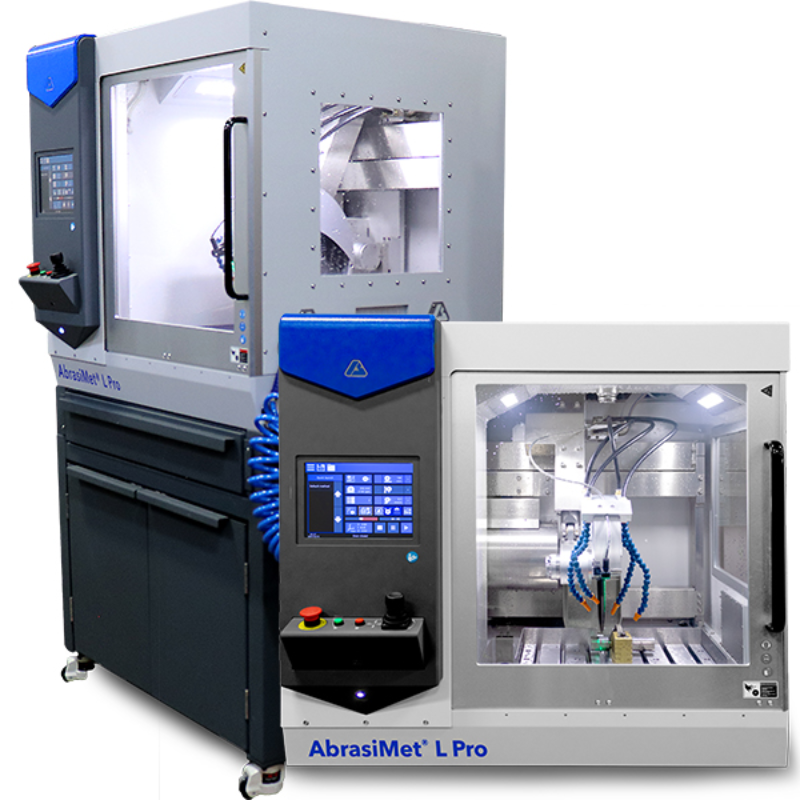

电子学是工程学的一个重要分支, 它是一门关于为了有用的目的而对电子进行控制的学科。运用物理学的知识得知, 电子的流动可以在真空、气体、或液体中进行,也可以在固体中受限制地流动(半导体)、接近不受限制地流动(导体)、或完全不受限制地流动(超导体)。 当今, 电子产品正变得越来越复杂,工程技术人员总是力图将许多部件放在一个小小的“黑匣子”中。制造商总是想把大部分资金用在改善其生产设施,而只愿意留下很少一部分资金用于质量控制。最坏的情况是,大多数公司宁愿把他们的质量控制资金用于基本设备投资,例如购买新型扫描电子显微镜、透射电子显微镜,或是厄歇谱仪,只剩下很少一部分钱用来购买试样制备设备和消耗器材。一个众所周知的现象就是人们对试样制备的重要性一直不够重视。 另一方面, 毫无疑问,最终产品的质量和可靠性取决于每个部件的性能。然而,这也总是电子工业的一个令人头痛的问题。对电子产品的截面进行金相检验是一种众所周知并通常广为接受的检验方法。 然而,大多数电子产品的金相技术人员可能面临的一个问题就是他们需要进行磨光和抛光的材料比预期的复杂和困难。他们也许从来没有学习过如何去处理多层基体材料,而他们在大学学习时只学过如何恰当地制备均匀的材料,例如钢、铜合金或铝合金。此外,他们还须面对设备很差的金相实验室,消耗器材的品种也很有限,并且使用所谓的“传统或常规方法”来制备先进的电子产品试样。 一般情况下,常规试样制备方法是从240#碳化硅砂纸开始,先进行磨成平面工序,接着使用600#、1200#砂纸,然后用0.3 m 氧化铝进行粗抛光,以及0.05 m 氧化铝在长绒毛织物上进行最终抛光,这样可获得光亮的表面。制备方法还可能因地而异,甚至还取决于实验室有哪些现成的消耗器材。当今,这种制备方法已经不适于用来制备先进材料。此外,他们也没有想到他们的试样是否好到足以和先进的显微镜或扫描电子显微镜相匹配。 在本文中,我们试图给出各种集成电路(IC)封装、引线连接,以及其它部件的试样制备方法。

打开失败或需在电脑查看,请在电脑上的资料中心栏目,点击"我的下载"。建议使用手机自带浏览器。

相关产品更多>>

下载该资料的还下载了

推荐学习更多>>

- 注意:

- 1、下载文件需消耗流量,最好在wifi的环境中下载,如果使用3G、4G下载,请注意文件大小。

- 2、下载的文件一般是pdf、word文件,下载后如不能直接浏览,可到应用商店中下载相应的阅读器APP。

- 3、下载的文件如需解压缩,如果手机没有安装解压缩软件,可到应用商店中下载相应的解压缩APP。