成都成英特尔全球最大芯片封装测试中心之一

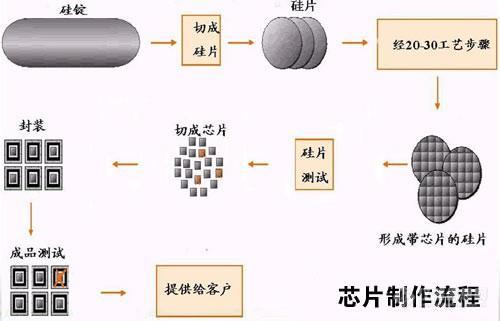

新华网成都3月26日电 26日,英特尔成都芯片封装测试厂第4.8亿颗芯片下线,最先进的2010全新酷睿移动处理器正式投产。至此,成都成为英特尔全球最大芯片封装测试中心之一。 作为中国唯一的英特尔芯片封装测试中心,成都厂已封装测试4.8亿颗芯片,确立了其在英特尔全球布局中的重要地位。2010年下半年,成都工厂还将建设成为英特尔全球集中进行晶圆预处理的三大工厂之一,成为全球封装测试来料的重要供应基地。 2009年,英特尔成都封装测试工厂年出口额约占成都出口加工区总额的80%,占四川省加工贸易出口的约30%。成都市委副书记唐川平表示,英特尔落户成都后,对成都加快信息产业集群发展,吸引更多世界知名企业入驻起到积极作用,并助推成都及西部实现经济结构调整和产业升级,迈向世界高新技术产业行列。 2003年8月,英特尔宣布投资建设英特尔成都芯片封装测试中心。截至目前,英特尔不断扩大成都厂的生产能力,在成都的总投资额已达到6亿美元。