蔡司推出半导体封装失效分析高分辨3D X射线成像解决方案

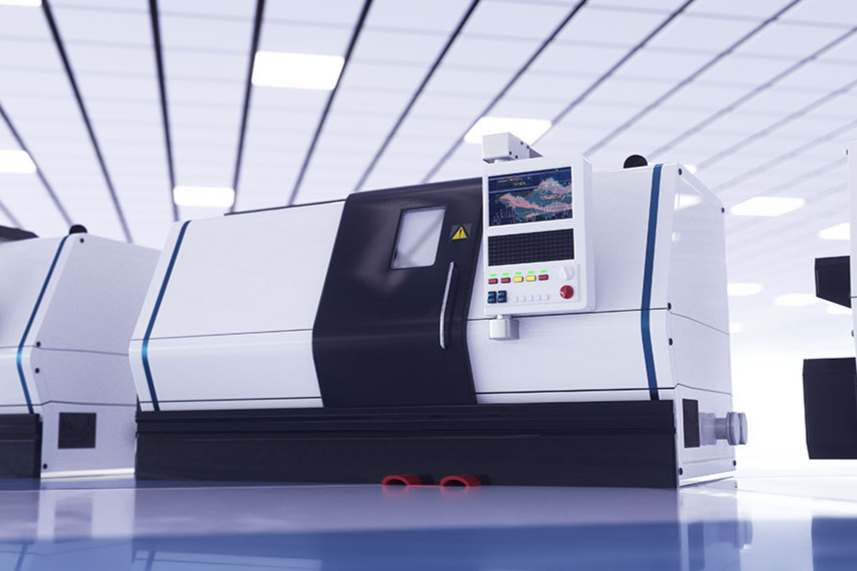

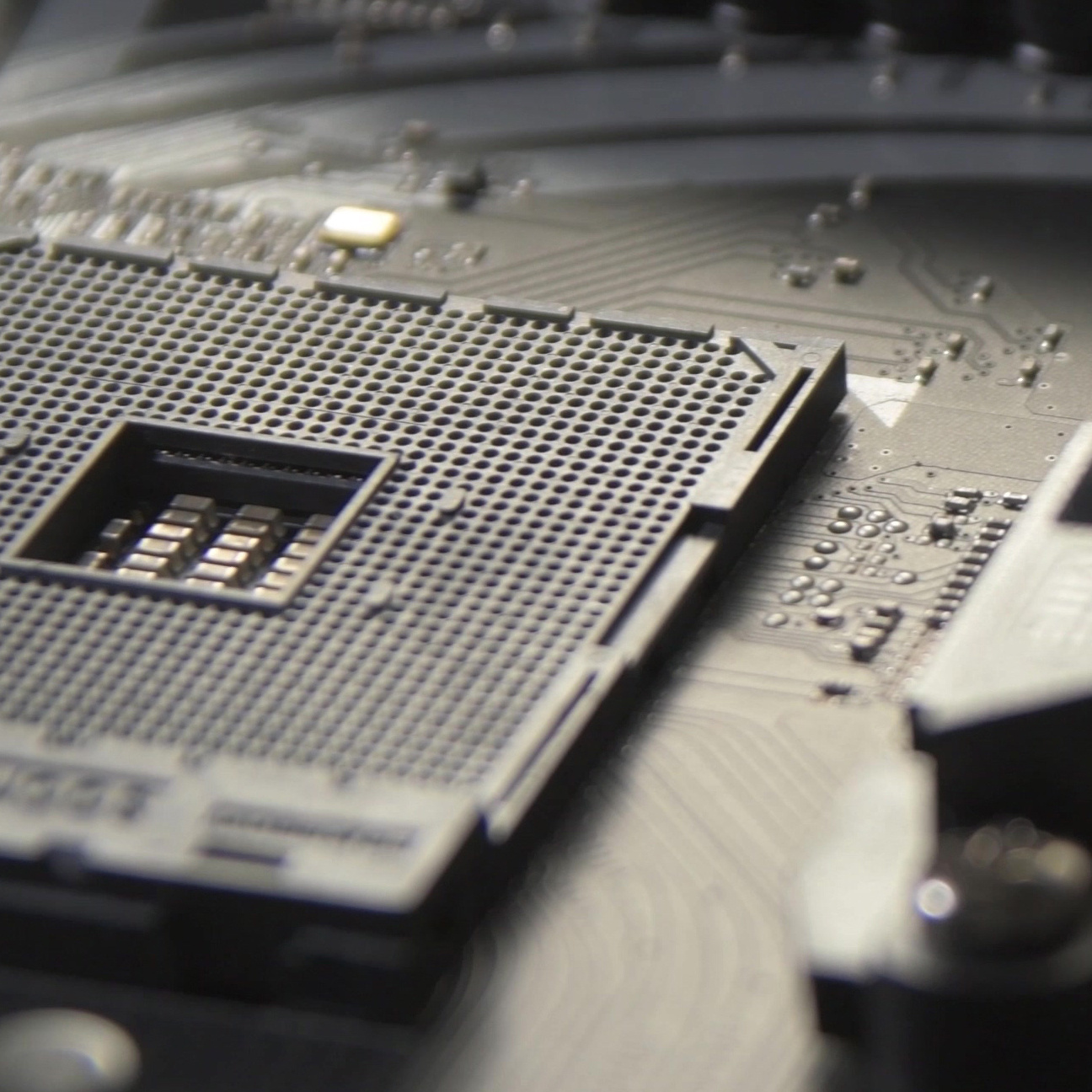

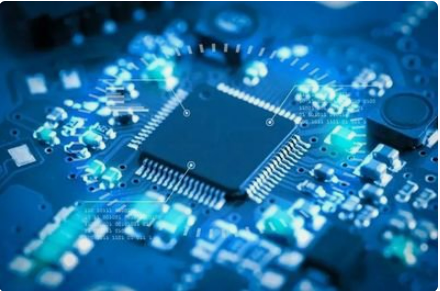

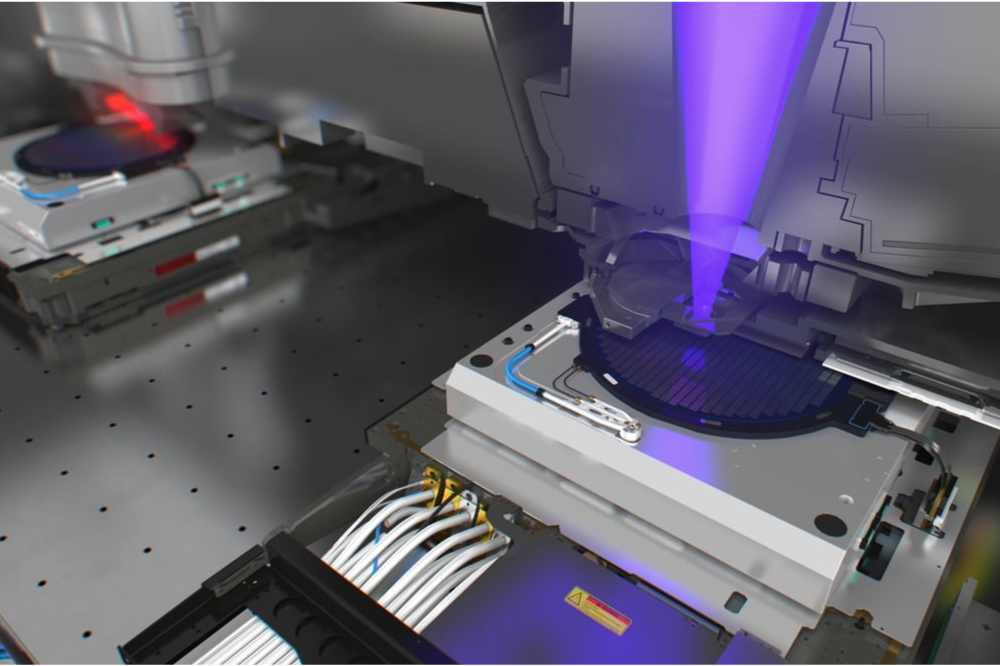

p 新型亚微米与纳米级XRM系统及新型microCT系统为失效分析提供了灵活选择,帮助客户加速技术发展,提高先进半导体封装的组装产量。 /p p strong 加州普莱斯顿与德国上科亨,2019年3月12日 /strong --蔡司发布了一套新型高分辨率3D X射线成像解决方案,用于包括2.5/3D与扩散型晶圆级封装在内的先进半导体封装的失效分析(FA)。蔡司X射线显微系统包括:通过亚微米级和纳米级高分辨率成像对封装产品进行失效分析的 a href=" https://www.instrument.com.cn/news/20190124/479353.shtml" target=" _blank" style=" color: rgb(0, 176, 240) text-decoration: underline " strong span style=" color: rgb(0, 176, 240) " Xradia 600 Versa系列 /span /strong /a 和 Xradia 800 Ultra X射线显微镜(XRM),以及Xradia Context microCT。随着在现有产品基础上新设备的研发推出,现如今,蔡司可以为半导体行业提供一系列3D X射线成像技术辅助生产。 /p p 蔡司制程控制解决方案(PCS)部门与蔡司SMT部门总裁Raj Jammy博士介绍说:“在170年的历史中,蔡司始终致力于拓展科学研究的疆域,推动成像技术的发展,以实现新的工业应用和技术创新。在今天的半导体行业,封装尺寸与器件尺寸越做越小,因此我们比以往任何时候都更需要新型成像解决方案,用于快速排除故障,实现更高的封装产量。蔡司很荣幸宣布推出这一新型先进半导体封装3D X射线成像解决方案,为客户提供强大的高分辨率成像分析设备,以提高失效分析准确率。” /p p strong 先进封装技术需要新型缺陷检测与失效分析的方法 /strong /p p 随着半导体产业面临CMOS微缩极限的挑战,人们需要通过半导体封装技术弥合性能上的差距。为了继续生产更小巧、更快速、更低功耗的器件,半导体行业正在通过芯片的3D堆叠和其他新型封装方式尝试封装创新。这些创新催生了日益复杂的封装架构,带来了新的制造挑战,同时也增加了封装故障的风险。此外,由于发生故障的位置往往隐藏于复杂的三维结构之中,传统的故障位置确认方法难以满足高效分析的需求。行业需要新型技术来有效地筛选和确定产生故障的根本原因。 /p p 为满足这一需求,蔡司开发出全新3D X射线成像解决方案,提供亚微米与纳米级3D图像,显示出隐藏于完整的封装3D结构中的特性与缺陷。将样品置于系统,样品在光路中旋转,从不同角度捕捉一系列2D X射线投影图像,然后使用复杂的数学模型和算法重建3D模型。新型解决方案可以从任意角度观察3D模型虚拟切片,从而在进行物理失效分析(PFA)之前对缺陷进行三维可视化。蔡司亚微米和纳米级XRM解决方案相结合,为客户提供独特的故障分析工作流程,有助于显著提高失效分析成功率。蔡司的新型Xradia Context microCT采用基于投影的几何放大技术,在大视场中实现高衬度和高分辨率成像,而且也可以全面升级至Xradia Versa X射线显微镜。 /p p strong 新型成像解决方案详解 /strong /p p a href=" https://www.instrument.com.cn/news/20190124/479353.shtml" target=" _blank" style=" color: rgb(0, 176, 240) text-decoration: underline " span style=" color: rgb(0, 176, 240) " strong Xradia 600 Versa /strong /span /a 系列是新一代3D XRM,能够在完整的已封装半导体器件中对已定位的缺陷进行无损成像。在结构化分析和失效分析应用中,新型解决方案在制程开发、良率提升和工艺分析等方面表现出色。Xradia 600 Versa系列以屡获殊荣且具有大工作距离高分辨率(RAAD)特性的Versa X射线显微镜为基础,提供优异的成像性能,实现大工作距离下的大样品的高分辨率成像,用于为封装、电路板和300毫米晶圆生产确定产生缺陷与故障的原因。利用该解决方案,可以轻松看到与封装级故障相关的缺陷,例如凸块或微型凸块中的裂纹、焊料润湿或硅通孔(TSV)空隙。在进行物理失效分析之前对缺陷进行3D可视化处理,有助于减少伪影,提供横纵方向的虚拟切片效果,从而提高失效分析成功率。新型解决方案的主要特性包括: /p p ◆最高空间分辨率0.5微米,最小体素40纳米 /p p ◆与Xradia 500 Versa系列相比, 工作效率提高了两倍,且在保证高分辨率的同时,在整个kV(电压)和功率范围内保持出色的X射线源焦点尺寸稳定性与热稳定性 /p p ◆更加简便易用,包括快速激活源 /p p ◆可靠性测试中可实现多个位点连续成像,并能观察封装结构内部亚微米结构变化 /p p style=" text-align: center" img src=" https://img1.17img.cn/17img/images/201903/uepic/fcb3b14e-afb6-4859-b117-ade3ce9e1694.jpg" title=" 1.jpg" alt=" 1.jpg" / /p p strong Xradia 800 Ultra /strong 将3D XRM提升至纳米级尺度,并在纳米尺寸下探索隐藏的特性,获得高空间分辨率图像的同时保持感兴趣区域的结构完整性。其应用包括超密间距覆晶与凸块连接的工艺分析、结构分析和缺陷分析,从而改进超密间距封装与后段制程(BEOL)互连的工艺改进。Xradia 800 Ultra能够对密间距铜柱微凸块中的金属间化合物所消耗焊料的结构和体积进行可视化。在成像过程中保留缺陷部位,有助于采用其他技术进行针对性的后期分析。还可以利用3D图像来表征盲孔组件(blind assemblies)的结构质量,例如晶圆对晶圆键合互连与直接混合键合等。该解决方案的主要特性包括: /p p ◆空间分辨率150纳米与50纳米(需要制备样品) /p p ◆选配皮秒激光样品制备工具,能够在一小时内提取完整体积(结构)样品(通常直径为100微米) /p p ◆兼容多种后续分析方法,包括透射电子显微镜(TEM)、能量色散X射线谱(EDS)、原子力显微镜(AFM)、二次离子质谱(SIMS)和纳米探针 /p p style=" text-align: center" img src=" https://img1.17img.cn/17img/images/201903/uepic/52ac92be-9189-4c80-bd09-b60d7bb9da1b.jpg" title=" 2.jpg" alt=" 2.jpg" / /p p strong Xradia Context microCT /strong 是一种基于Versa平台的新型亚微米分辨率3D X射线microCT系统。该解决方案用于封装产品在小工作距离和高通量下进行高分辨率成像。主要特性包括: /p p ◆在大视场下提供大样品的全视场成像(体积比Xradia Versa XRM系统大10倍) /p p ◆小像素尺寸的高像素密度探测器(六百万像素)即使在观察视野较大的情况下也能确保较高分辨率 /p p ◆X射线microCT拥有空间分辨率0.95微米,最小体素0.5微米 /p p ◆出色的图像质量与衬度 /p p ◆可升级为Xradia Versa,实现RaaD功能,对完整大样品进行高分辨率成像 /p p style=" text-align: center" img src=" https://img1.17img.cn/17img/images/201903/uepic/a444699e-2096-43cc-a3ed-3471855ecc79.jpg" title=" 3.jpg" alt=" 3.jpg" / /p p 上海新国际博览中心即将于3月20日至22日举办中国半导体展(SEMICON China),蔡司将在展会上展示最新显微镜产品和解决方案,包括新型Xradia 600 Versa系列、Xradia 800 Ultra和Xradia Context microCT系统。如有意了解详情,您可到N2展厅2619号展位参观蔡司展品。 /p p strong 关于蔡司 /strong /p p 蔡司是全球光学和光电领域的先锋。上个财年度,蔡司集团旗下四个部门的总收入超过58亿欧元,包括工业质量与研究、医疗技术、消费市场,以及半导体制造技术(截止:2018年9月30日)。 /p p 蔡司为客户开发、生产和分销用于工业测量与质量控制的创新解决方案,用于生命科学和材料研究的显微镜解决方案,以及用于眼科和显微外科诊断与治疗的医疗技术解决方案。在半导体行业,“蔡司”已成为世界优秀的光学光刻技术的代名词,该技术被芯片行业用于制造半导体元件。眼镜镜片、照相机镜片和双筒望远镜等引领行业潮流的蔡司产品正在全球市场热销。 /p p 凭借与数字化、医疗保健和智能生产等未来增长领域相结合的投资组合,以及强大的品牌,蔡司正在塑造光学和光电行业以外的未来。该公司在研发方面的重大、可持续投资为蔡司技术和市场成功保持领先地位和持续扩张奠定了基础。 /p p 蔡司拥有约30,000名员工,活跃于全球近50个国家,拥有约60家自有销售和服务公司、30多家生产基地和约25家开发基地。公司于1846年创办于耶拿(Jena),总部位于德国上科亨。卡尔· 蔡司基金会(Carl Zeiss Foundation)是德国最大的基金会之一,致力于促进科学发展,是控股公司卡尔· 蔡司股份公司的唯一所有者。 /p