发改委:加快在光刻胶、大尺寸硅片、电子封装材料等领域实现突破

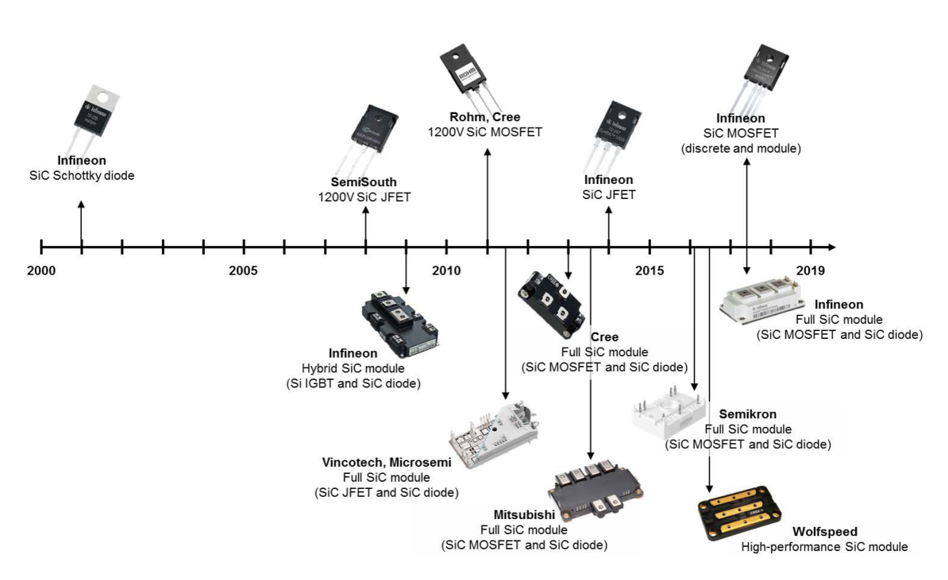

p style=" text-align: justify text-indent: 2em margin-top: 10px line-height: 1.5em " strong 仪器信息网讯 /strong 9月25日,中华人民共和国国家发展和改革委员会发布 a href=" https://www.ndrc.gov.cn/xwdt/tzgg/202009/t20200925_1239583.html" target=" _self" 《关于扩大战略性新兴产业投资培育壮大新增长点增长极的指导意见》 /a (发改高技〔2020〕1409号,以下简称《指导意见》)。 /p p style=" text-align: justify text-indent: 2em margin-top: 10px line-height: 1.5em " 本次《指导意见》针对扩大战略性新兴产业投资提出了三方面重点任务:一是聚焦重点产业投资领域;二是打造产业集聚发展新高地;三是增强资金保障能力。《指导意见》围绕优化投资服务环境,提出了四方面政策保障措施:一是深化“放管服”改革;二是优化项目要素配置;三是完善包容审慎监管;四是营造良好投资氛围。覆盖的重点产业投资领域涵盖信息技术产业,生物产业,高端装备制造产业,新材料产业,新能源产业,智能及新能源汽车产业,节能环保产业和数字创意产业。 /p p style=" text-align: justify text-indent: 2em margin-top: 10px line-height: 1.5em " 其中明确提出“围绕保障大飞机、 strong span style=" color: rgb(255, 0, 0) " 微电子制造 /span /strong 、深海采矿等重点领域产业链供应链稳定,加快在 strong span style=" color: rgb(255, 0, 0) " 光刻胶 /span /strong 、高纯靶材、高温合金、高性能纤维材料、高强高导耐热材料、耐腐蚀材料、 strong span style=" color: rgb(255, 0, 0) " 大尺寸硅片、电子封装材料 /span /strong 等领域实现突破”,“加快主轴承、 strong span style=" color: rgb(255, 0, 0) " IGBT /span /strong 、控制系统、高压直流海底电缆等核心技术部件研发”。光刻胶、大尺寸硅片和电子封装材料是半导体产业的关键技术领域,而IGBT更是涉及第三代半导体产业的重要半导体器件。此外,信息技术产业、高端装备制造产业和智能及新能源汽车产业更是有赖于半导体产业。本次《指导意见》的出台,半导体产业将再迎利好。 /p p style=" text-align: justify text-indent: 2em margin-top: 10px line-height: 1.5em " 以下为《指导意见》全文: /p div style=" margin: 0px auto padding: 0px box-sizing: border-box text-align: center " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " white-space:=" " text-align:=" " line-height:=" " 1.5=" " span style=" margin: 0px auto padding: 0px box-sizing: border-box font-size: 24px font-family: arial, helvetica, sans-serif line-height: 1.5 !important " strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " font-size:=" " 16px=" " line-height:=" " 1.5=" " 关于扩大战略性新兴产业投资 /strong /span /div p span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " /span /p div style=" margin: 0px auto padding: 0px box-sizing: border-box text-align: center font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " strong style=" margin: 0px padding: 0px box-sizing: border-box line-height: 1.5 !important " span style=" margin: 0px auto padding: 0px box-sizing: border-box font-size: 24px line-height: 1.5 !important " 培育壮大新增长点增长极的指导意 /span /strong strong style=" margin: 0px padding: 0px box-sizing: border-box line-height: 1.5 !important " span style=" margin: 0px auto padding: 0px box-sizing: border-box font-size: 24px line-height: 1.5 !important " 见 /span /strong /div p style=" text-indent: 0em " span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " /span /p div style=" margin: 0px auto padding: 0px box-sizing: border-box text-align: center font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " 发改高技〔2020〕1409号 /div p style=" text-align: justify " br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " 国务院有关部门,各省、自治区、直辖市、新疆生产建设兵团发展改革委、科技厅(委、局)、工业和信息化委(厅)、财政厅(局): /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " & nbsp 为深入贯彻落实党中央、国务院关于在常态化疫情防控中扎实做好“六稳”工作,全面落实“六保”任务,扩大战略性新兴产业投资、培育壮大新的增长点增长极的决策部署,更好发挥战略性新兴产业重要引擎作用,加快构建现代化产业体系,推动经济高质量发展,现提出如下意见: /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " span style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " & nbsp /span strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " 一、总体要求 /strong /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " & nbsp 以习近平新时代中国特色社会主义思想为指导,全面贯彻党的十九大和十九届二中、三中、四中全会精神,统筹做好疫情防控和经济社会发展工作,坚定不移贯彻新发展理念,围绕重点产业链、龙头企业、重大投资项目,加强要素保障,促进上下游、产供销、大中小企业协同,加快推动战略性新兴产业高质量发展,培育壮大经济发展新动能。 /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " span style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " & nbsp /span strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " ——聚焦重点产业领域。 /strong 着力扬优势、补短板、强弱项,加快适应、引领、创造新需求,推动重点产业领域形成规模效应。 /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " span style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " & nbsp /span strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " ——打造集聚发展高地。 /strong 充分发挥产业集群要素资源集聚、产业协同高效、产业生态完备等优势,利用好自由贸易试验区、自由贸易港等开放平台,促进形成新的区域增长极。 /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " span style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " & nbsp /span strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " ——增强要素保障能力。 /strong 按照“资金跟着项目走、要素跟着项目走”原则,引导人才、用地、用能等要素合理配置、有效集聚。 /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " span style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " & nbsp /span strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " ——优化投资服务环境。 /strong 通过优化营商环境、加大财政金融支持、创新投资模式,畅通供需对接渠道,释放市场活力和投资潜力。 /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " span style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " & nbsp /span strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " 二、聚焦重点产业投资领域 /strong /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " span style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " & nbsp /span strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (一)加快新一代信息技术产业提质增效。 /strong 加大5G建设投资,加快5G商用发展步伐,将各级政府机关、企事业单位、公共机构优先向基站建设开放,研究推动将5G基站纳入商业楼宇、居民住宅建设规范。加快基础材料、关键芯片、高端元器件、新型显示器件、关键软件等核心技术攻关,大力推动重点工程和重大项目建设,积极扩大合理有效投资。稳步推进工业互联网、人工智能、物联网、车联网、大数据、云计算、区块链等技术集成创新和融合应用。加快推进基于信息化、数字化、智能化的新型城市基础设施建设。围绕智慧广电、媒体融合、5G广播、智慧水利、智慧港口、智慧物流、智慧市政、智慧社区、智慧家政、智慧旅游、在线消费、在线教育、医疗健康等成长潜力大的新兴方向,实施中小企业数字化赋能专项行动,推动中小微企业“上云用数赋智”,培育形成一批支柱性产业。实施数字乡村发展战略,加快补全农村互联网基础设施短板,加强数字乡村产业体系建设,鼓励开发满足农民生产生活需求的信息化产品和应用,发展农村互联网新业态新模式。实施“互联网+”农产品出村进城工程,推进农业农村大数据中心和重要农产品全产业链大数据建设,加快农业全产业链的数字化转型。 strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (责任部门:发展改革委、工业和信息化部、科技部、教育部、住房城乡建设部、交通运输部、水利部、农业农村部、商务部、卫生健康委、广电总局、国铁集团等按职责分工负责) /strong /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " span style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " & nbsp /span strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (二)加快生物产业创新发展步伐。 /strong 加快推动创新疫苗、体外诊断与检测试剂、抗体药物等产业重大工程和项目落实落地,鼓励疫苗品种及工艺升级换代。系统规划国家生物安全风险防控和治理体系建设,加大生物安全与应急领域投资,加强国家生物制品检验检定创新平台建设,支持遗传细胞与遗传育种技术研发中心、合成生物技术创新中心、生物药技术创新中心建设,促进生物技术健康发展。改革完善中药审评审批机制,促进中药新药研发和产业发展。实施生物技术惠民工程,为自主创新药品、医疗装备等产品创造市场。 strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (责任部门:发展改革委、卫生健康委、科技部、工业和信息化部、中医药局、药监局等按职责分工负责) /strong /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " span style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " & nbsp /span strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (三)加快高端装备制造产业补短板。 /strong 重点支持工业机器人、建筑、医疗等特种机器人、高端仪器仪表、轨道交通装备、高档五轴数控机床、节能异步牵引电动机、高端医疗装备和制药装备、航空航天装备、海洋工程装备及高技术船舶等高端装备生产,实施智能制造、智能建造试点示范。研发推广城市市政基础设施运维、农业生产专用传感器、智能装备、自动化系统和管理平台,建设一批创新中心和示范基地、试点县。鼓励龙头企业建设“互联网+”协同制造示范工厂,建立高标准工业互联网平台。 strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (责任部门:发展改革委、工业和信息化部、住房城乡建设部、农业农村部、国铁集团等按职责分工负责) /strong /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " span style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " & nbsp /span strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (四)加快新材料产业强弱项。 /strong 围绕保障大飞机、微电子制造、深海采矿等重点领域产业链供应链稳定,加快在光刻胶、高纯靶材、高温合金、高性能纤维材料、高强高导耐热材料、耐腐蚀材料、大尺寸硅片、电子封装材料等领域实现突破。实施新材料创新发展行动计划,提升稀土、钒钛、钨钼、锂、铷铯、石墨等特色资源在开采、冶炼、深加工等环节的技术水平,加快拓展石墨烯、纳米材料等在光电子、航空装备、新能源、生物医药等领域的应用。 strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (责任部门:发展改革委、工业和信息化部等按职责分工负责) /strong /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " span style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " & nbsp /span strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (五)加快新能源产业跨越式发展。 /strong 聚焦新能源装备制造“卡脖子”问题,加快主轴承、IGBT、控制系统、高压直流海底电缆等核心技术部件研发。加快突破风光水储互补、先进燃料电池、高效储能与海洋能发电等新能源电力技术瓶颈,建设智能电网、微电网、分布式能源、新型储能、制氢加氢设施、燃料电池系统等基础设施网络。提升先进燃煤发电、核能、非常规油气勘探开发等基础设施网络的数字化、智能化水平。大力开展综合能源服务,推动源网荷储协同互动,有条件的地区开展秸秆能源化利用。 strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (责任部门:发展改革委、工业和信息化部、自然资源部、能源局等按职责分工负责) /strong /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " span style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " & nbsp /span strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (六)加快智能及新能源汽车产业基础支撑能力建设。 /strong 开展公共领域车辆全面电动化城市示范,提高城市公交、出租、环卫、城市物流配送等领域车辆电动化比例。加快新能源汽车充/换电站建设,提升高速公路服务区和公共停车位的快速充/换电站覆盖率。实施智能网联汽车道路测试和示范应用,加大车联网车路协同基础设施建设力度,加快智能汽车特定场景应用和产业化发展。支持建设一批自动驾驶运营大数据中心。以支撑智能汽车应用和改善出行为切入点,建设城市道路、建筑、公共设施融合感知体系,打造基于城市信息模型(CIM)、融合城市动态和静态数据于一体的“车城网”平台,推动智能汽车与智慧城市协同发展。 strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (责任部门:发展改革委、工业和信息化部、住房城乡建设部、交通运输部等按职责分工负责) /strong /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " span style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " & nbsp /span strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (七)加快节能环保产业试点示范。 /strong 实施城市绿色发展综合示范工程,支持有条件的地区结合城市更新和城镇老旧小区改造,开展城市生态环境改善和小区内建筑节能节水改造及相关设施改造提升,推广节水效益分享等合同节水管理典型模式,鼓励创新发展合同节水管理商业模式,推动节水服务产业发展。开展共用物流集装化体系示范,实现仓储物流标准化周转箱高效循环利用。组织开展多式联运示范工程建设。发展智慧农业,推进农业生产环境自动监测、生产过程智能管理。试点在超大城市建立基于人工智能与区块链技术的生态环境新型治理体系。探索开展环境综合治理托管、生态环境导向的开发(EOD)模式等环境治理模式创新,提升环境治理服务水平,推动环保产业持续发展。加大节能、节水环保装备产业和海水淡化产业培育力度,加快先进技术装备示范和推广应用。实施绿色消费示范,鼓励绿色出行、绿色商场、绿色饭店、绿色电商等绿色流通主体加快发展。积极推行绿色建造,加快推动智能建造与建筑工业化协同发展,大力发展钢结构建筑,提高资源利用效率,大幅降低能耗、物耗和水耗水平。 strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (责任部门:发展改革委、科技部、工业和信息化部、自然资源部、生态环境部、住房和城乡建设部、交通运输部、农业农村部、商务部、国铁集团等按职责分工负责) /strong /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " span style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " & nbsp /span strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (八)加快数字创意产业融合发展。 /strong 鼓励数字创意产业与生产制造、文化教育、旅游体育、健康医疗与养老、智慧农业等领域融合发展,激发市场消费活力。建设一批数字创意产业集群,加强数字内容供给和技术装备研发平台,打造高水平直播和短视频基地、一流电竞中心、高沉浸式产品体验展示中心,提供VR旅游、AR营销、数字文博馆、创意设计、智慧广电、智能体育等多元化消费体验。发展高清电视、超高清电视和5G高新视频,发挥网络视听平台和产业园区融合集聚作用,贯通内容生产传播价值链和电子信息设备产业链,联动线上线下文化娱乐和综合信息消费,构建新时代大视听全产业链市场发展格局。 strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (责任部门:发展改革委、教育部、工业和信息化部、农业农村部、文化和旅游部、广电总局、体育总局等按职责分工负责) /strong /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " span style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " & nbsp /span strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " 三、打造产业集聚发展新高地 /strong /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " span style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " & nbsp /span strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (九)深入推进国家战略性新兴产业集群发展工程。 /strong 构建产业集群梯次发展体系,培育和打造10个具有全球影响力的战略性新兴产业基地、100个具备国际竞争力的战略性新兴产业集群,引导和储备1000个各具特色的战略性新兴产业生态,形成分工明确、相互衔接的发展格局。适时启动新一批国家战略性新兴产业集群建设。培育若干世界级先进制造业集群。综合运用财政、土地、金融、科技、人才、知识产权等政策,协同支持产业集群建设、领军企业培育、关键技术研发和人才培养等项目。 strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (责任部门:发展改革委、科技部、工业和信息化部、财政部、人力资源社会保障部、自然资源部、商务部、人民银行、知识产权局等按职责分工负责) /strong /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " span style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " & nbsp /span strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (十)增强产业集群创新引领力。 /strong 启动实施产业集群创新能力提升工程。发挥科技创新中心、综合性国家科学中心创新资源丰富的优势,推动特色产业集群发展壮大。依托集群内优势产学研单位联合建设一批产业创新中心、工程研究中心、产业计量测试中心、质检中心、企业技术中心、标准创新基地、技术创新中心、制造业创新中心、产业知识产权运营中心等创新平台和重点地区承接产业转移平台。推动产业链关键环节企业建设产业集群协同创新中心和产业研究院。 strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (责任部门:发展改革委、科技部、工业和信息化部、市场监管总局、中科院、知识产权局等按职责分工负责) /strong /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " & nbsp ( strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " 十一)推进产城深度融合。 /strong 启动实施产业集群产城融合示范工程。以产业集群建设推动生产、生活、生态融合发展,促进加快形成创新引领、要素富集、空间集约、宜居宜业的产业生态综合体。加快产业集群交通、物流、生态环保、水利等基础设施数字化改造。推进产业集群资源环境设施共建共享、能源资源智能利用、污染物集中处理等设施建设。探索“核心承载区管理机构+投资建设公司+专业运营公司”建设新模式,推进核心承载区加快向企业综合服务、产业链资源整合、价值再造平台转型。推动符合条件的战略性新兴产业集群通过市场化方式开展基础设施领域不动产投资信托基金(REITs)试点。 strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (责任部门:发展改革委、住房城乡建设部、交通运输部、水利部、证监会、国铁集团等按职责分工负责) /strong /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " span style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " & nbsp /span strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (十二)聚焦产业集群应用场景营造。 /strong 启动实施产业集群应用场景建设工程。围绕5G、人工智能、车联网、大数据、区块链、工业互联网等领域,率先在具备条件的集群内试点建设一批应用场景示范工程,定期面向特定市场主体发布应用场景项目清单,择优评选若干新兴产业应用场景进行示范推广,并给予应用方一定支持。鼓励集群内企业发展面向定制化应用场景的“产品+服务”模式,创新自主知识产权产品推广应用方式和可再生能源综合应用,壮大国内产业循环。 strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (责任部门:发展改革委、工业和信息化部、住房城乡建设部、能源局、知识产权局等按职责分工负责) /strong /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " span style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " & nbsp /span strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (十三)提高产业集群公共服务能力。 /strong 实施产业集群公共服务能力提升工程。依托行业协会、专业机构、科研单位等建设一批专业化产业集群促进机构。推进国家标准参考数据体系建设。建设产业集群创新和公共服务综合体,强化研发设计、计量测试、标准认证、中试验证、检验检测、智能制造、产业互联网、创新转化等产业公共服务平台支撑,打造集技术转移、产业加速、孵化转化等为一体的高品质产业空间。在智能制造、绿色制造、工业互联网等领域培育一批解决方案供应商。支持有条件的集群聚焦新兴应用开展5G、数据中心、人工智能、工业互联网、车联网、物联网等新型基础设施建设。 strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (责任部门:发展改革委、工业和信息化部、住房城乡建设部、商务部、市场监管总局、中科院等按职责分工负责) /strong /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " span style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " & nbsp /span strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " 四、增强资金保障能力 /strong /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " span style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " & nbsp /span strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (十四)加强政府资金引导。 /strong 统筹用好各级各类政府资金、创业投资和政府出资产业投资基金,创新政府资金支持方式,强化对战略性新兴产业重大工程项目的投资牵引作用。鼓励地方政府设立战略性新兴产业专项资金计划,按市场化方式引导带动社会资本设立产业投资基金。围绕保障重点领域产业链供应链稳定,鼓励建立中小微企业信贷风险补偿机制,加大对战略性新兴产业的支持力度。 strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (责任部门:发展改革委、工业和信息化部、财政部等按职责分工负责) /strong /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " span style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " & nbsp /span strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (十五)提升金融服务水平。 /strong 鼓励金融机构创新开发适应战略性新兴产业特点的金融产品和服务,加大对产业链核心企业的支持力度,优化产业链上下游企业金融服务,完善内部考核和风险控制机制。鼓励银行探索建立新兴产业金融服务中心或事业部。推动政银企合作。构建保险等中长期资金投资战略性新兴产业的有效机制。制订战略性新兴产业上市公司分类指引,优化发行上市制度,加大科创板等对战略性新兴产业的支持力度。加大战略性新兴产业企业(公司)债券发行力度。支持创业投资、私募基金等投资战略性新兴产业。 strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (责任部门:人民银行、银保监会、证监会、发展改革委等按职责分工负责) /strong /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " span style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " & nbsp /span strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (十六)推进市场主体投资。 /strong 依托国有企业主业优势,优化国有经济布局和结构,加大战略性新兴产业投资布局力度。鼓励具备条件的各类所有制企业独立或联合承担国家各类战略性新兴产业研发、创新能力和产业化等建设项目。支持各类所有制企业发挥各自优势,加强在战略性新兴产业领域合作,促进大中小企业融通发展。修订外商投资准入负面清单和鼓励外商投资产业目录,进一步放宽或取消外商投资限制,增加战略性新兴产业条目。 strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (责任部门:发展改革委、工业和信息化部、商务部、国资委等职责分工负责) /strong /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " span style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " & nbsp /span strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " 五、优化投资服务环境 /strong /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " span style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " & nbsp /span strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (十七)深化“放管服”改革。 /strong 全力推动重大项目“物流通、资金通、人员通、政策通”。深化投资审批制度改革,推进战略性新兴产业投资项目承诺制审批,简化、整合项目报建手续,深化投资项目在线审批监管平台应用,加快推进全程网办。全面梳理新产业、新业态、新模式准入和行政许可流程,精简审批环节,缩短办理时限,推行“一网通办”。 strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (责任部门:发展改革委牵头,各部门按职责分工负责) /strong /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " span style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " & nbsp /span strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (十八)加快要素市场化配置。 /strong 充分发挥市场在资源配置中的决定性作用,更好发挥政府作用。统筹做好用地、用水、用能、环保等要素配置,将土地林地、建筑用砂、能耗等指标优先保障符合高质量发展要求的重大工程和项目需求。加强工业用地市场化配置,鼓励地方盘活利用存量土地。 strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (责任部门:发展改革委、自然资源部、生态环境部、住房城乡建设部、水利部、商务部等按职责分工负责) /strong /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " span style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " & nbsp /span strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (十九)完善包容审慎监管。 /strong 推动建立适应新业态新模式发展特点、以信用为基础的新型监管机制。规范行政执法行为,推进跨部门联合“双随机、一公开”监管和“互联网+监管”,细化量化行政处罚标准。 strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (责任部门:发展改革委牵头,各部门按职责分工负责) /strong /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " span style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " & nbsp /span strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (二十)营造良好投资氛围。 /strong 各地区、各部门要积极做好政策咨询和宣传引导工作,以“线上线下”产业招商会、优质项目遴选赛、政银企对接会、高端论坛等形式加强交流合作,增强企业投资意愿,激发社会投资创新动力和发展活力,努力营造全社会敢投资、愿投资、善投资战略性新兴产业发展的良好氛围。 strong style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " sans-serif=" " line-height:=" " 1.5=" " (责任部门:发展改革委牵头,各部门按职责分工负责)& nbsp /strong /span br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / br style=" margin: 0px padding: 0px box-sizing: border-box font-family: PingFangSC-Regular, " helvetica=" " hiragino=" " sans=" " microsoft=" " yahei=" " color:=" " text-align:=" " white-space:=" " line-height:=" " 1.5=" " / /p p br/ /p p br/ /p p style=" margin: 5px auto padding: 0px box-sizing: border-box text-align: center line-height: normal " span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun line-height: 1.5 !important " 国家发 /span span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun line-height: 1.5 !important " 展改革委 /span /p p style=" margin-top: 5px margin-bottom: 5px line-height: normal " span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun color: rgb(86, 88, 98) text-align: justify line-height: 1.5 !important " /span /p p style=" margin: 5px auto padding: 0px box-sizing: border-box text-align: center line-height: normal " span style=" margin: 0px auto padding: 0px box-sizing: border-box font-family: SimSun line-height: 1.5 !important " 科& nbsp 技& nbsp 部 /span /p p style=" margin: 5px auto padding: 0px box-sizing: border-box text-align: center line-height: normal " span style=" font-family: SimSun " 工业和信息化部 /span /p p style=" margin: 5px auto padding: 0px box-sizing: border-box text-align: center line-height: normal " span style=" font-family: SimSun color: rgb(86, 88, 98) " 财& nbsp 政& nbsp 部 /span /p p style=" margin: 5px auto padding: 0px box-sizing: border-box text-align: center line-height: normal " span style=" font-family: SimSun color: rgb(86, 88, 98) " 2020年9月8日 /span /p p br/ /p p br/ /p