东京电子成功开发可用于制造400层堆叠3D NAND芯片的新技术

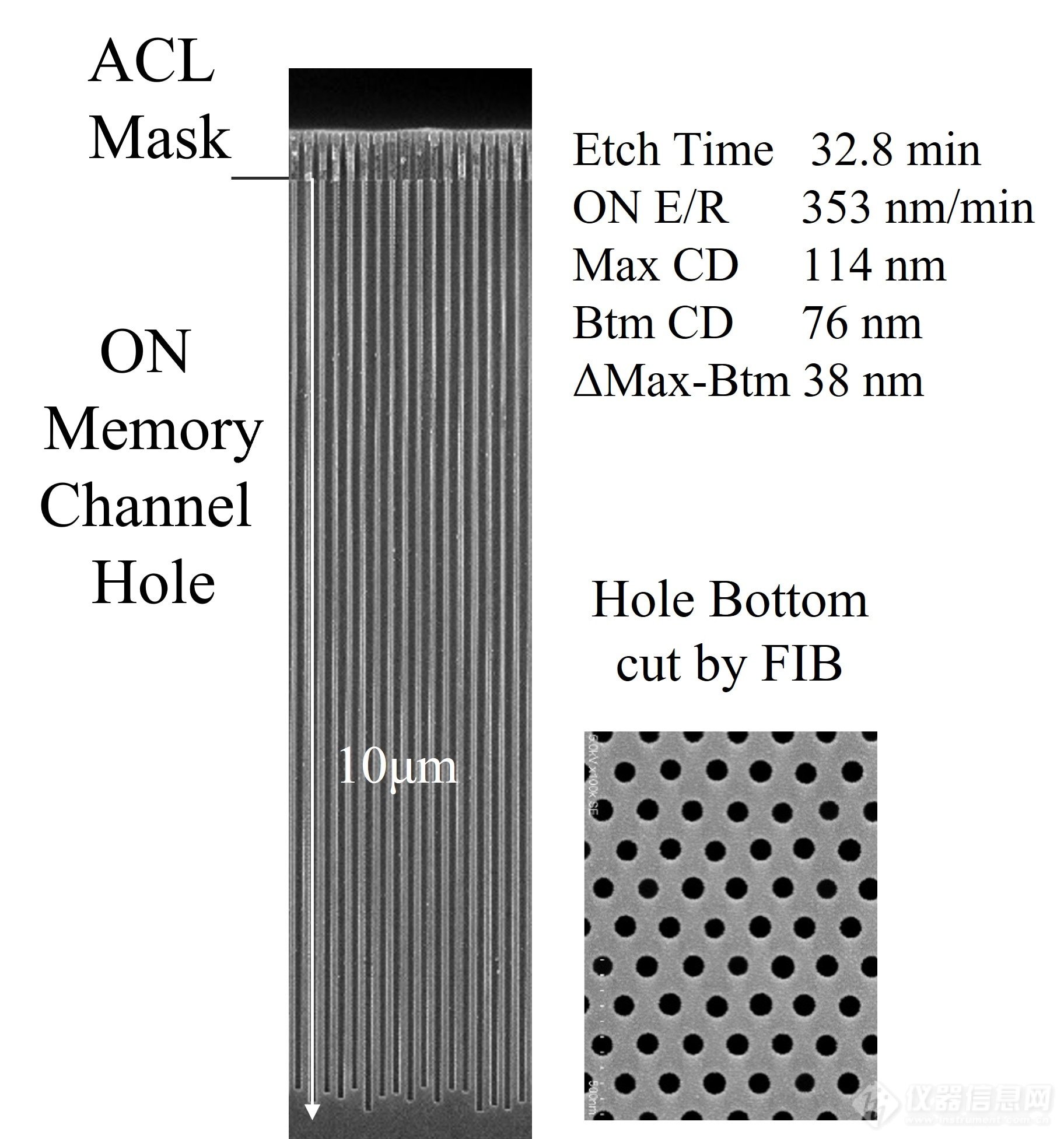

导读:东京电子开发了一种创新的蚀刻技术能够在堆叠超过400层的先进3D NAND器件中生产存储沟道孔,可以在33分钟内实现高深宽比的10µm深蚀刻。

半导体设备巨头东京电子近日宣布,其位于东京电子宫城的开发团队(其等离子体蚀刻系统的开发和制造基地)开发了一种创新的蚀刻技术,能够在堆叠超过400层的先进3D NAND器件中生产存储沟道孔。该团队开发的新工艺首次将介电蚀刻应用于低温范围,生产出具有极高蚀刻率的系统。这项创新技术不仅可以在33分钟内实现高深宽比的10µm深蚀刻,而且与以前的技术相比,还可以将全球变暖的可能性降低84%。蚀刻结构的几何形状非常明确,如图1所示。这项技术带来的潜在创新将推动更大容量的3D NAND闪存的开发。

图1.蚀刻后的存储器沟道孔图案的截面SEM图像和孔底部的FIB切割图像。

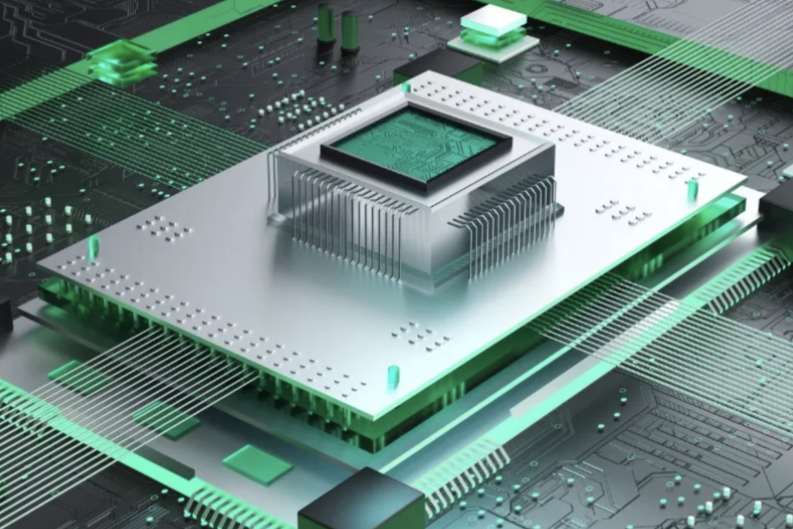

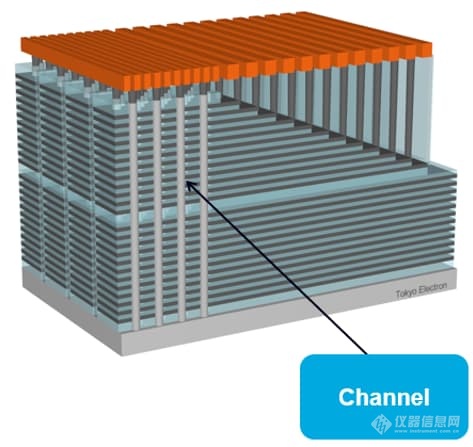

图2 3D NAND闪存

TEL开发这项技术的团队在6月11日至6月16日在京都举行的2023年超大规模集成电路技术与电路研讨会上提交其研究结果报告,该研讨会是最负盛名的半导体研究国际会议之一。

来源于:仪器信息网译

热门评论

最新资讯

新闻专题

更多推荐

写评论…

0