华虹宏力“用于晶圆芯片并行测试的模拟量测试焊盘排布结构”专利获授权

导读:华虹宏力获得专利,发明用于晶圆芯片并行测试的模拟量测试焊盘排布结构,旨在提高测试效率,减少成本,优化芯片性能,通过合理布局焊盘,实现并行测试,适应高集成度需求,减少对芯片面积的影响。

天眼查显示,上海华虹宏力半导体制造有限公司近日取得一项名为“用于晶圆芯片并行测试的模拟量测试焊盘排布结构”的专利,授权公告号为CN112147487B,授权公告日为2024年7月23日,申请日为2020年9月25日。

背景技术

在晶圆出厂前,需要对晶圆上的芯片进行测试,以判断芯片性能的好坏。在晶圆芯片测试中,目标晶圆被安装在测试机台上,其上目标芯片的测试焊盘(pad)通过探针卡与测试机台电性耦合,由测试机台通过执行测试指令,以完成对目标芯片的测试过程。测试完一个芯片,探针卡与下一目标芯片的测试焊盘电性耦合,以继续进行测试。

为了提高测试效率,降低测试成本,在进行晶圆芯片测试时,通常需要对晶圆上的芯片进行并行测试,即同一时间内对目标晶圆的多个目标芯片进行测试,或,在单个目标芯片上同步或异步运行多个测试任务,以同时完成对目标芯片多项参数的测试。

在进行晶圆芯片并行测试时,通常还需通过测量特定测试焊盘,以获取目标芯片的模拟电参数值,并对该目标芯片的模拟电参数进行调整。随着晶圆上芯片集成度的不断提高,目标芯片中需要调整的电参数的种类不断增多,因此所需的特定测试焊盘的数量也不断增加。

然而,相关技术中用于获取目标芯片模拟电参数值的测试焊盘,与目标芯片上的功能焊盘无法复用,需要单独制作,因此过多的测试焊盘会占用芯片的较大面积,对芯片的性能产生不利影响。

发明内容

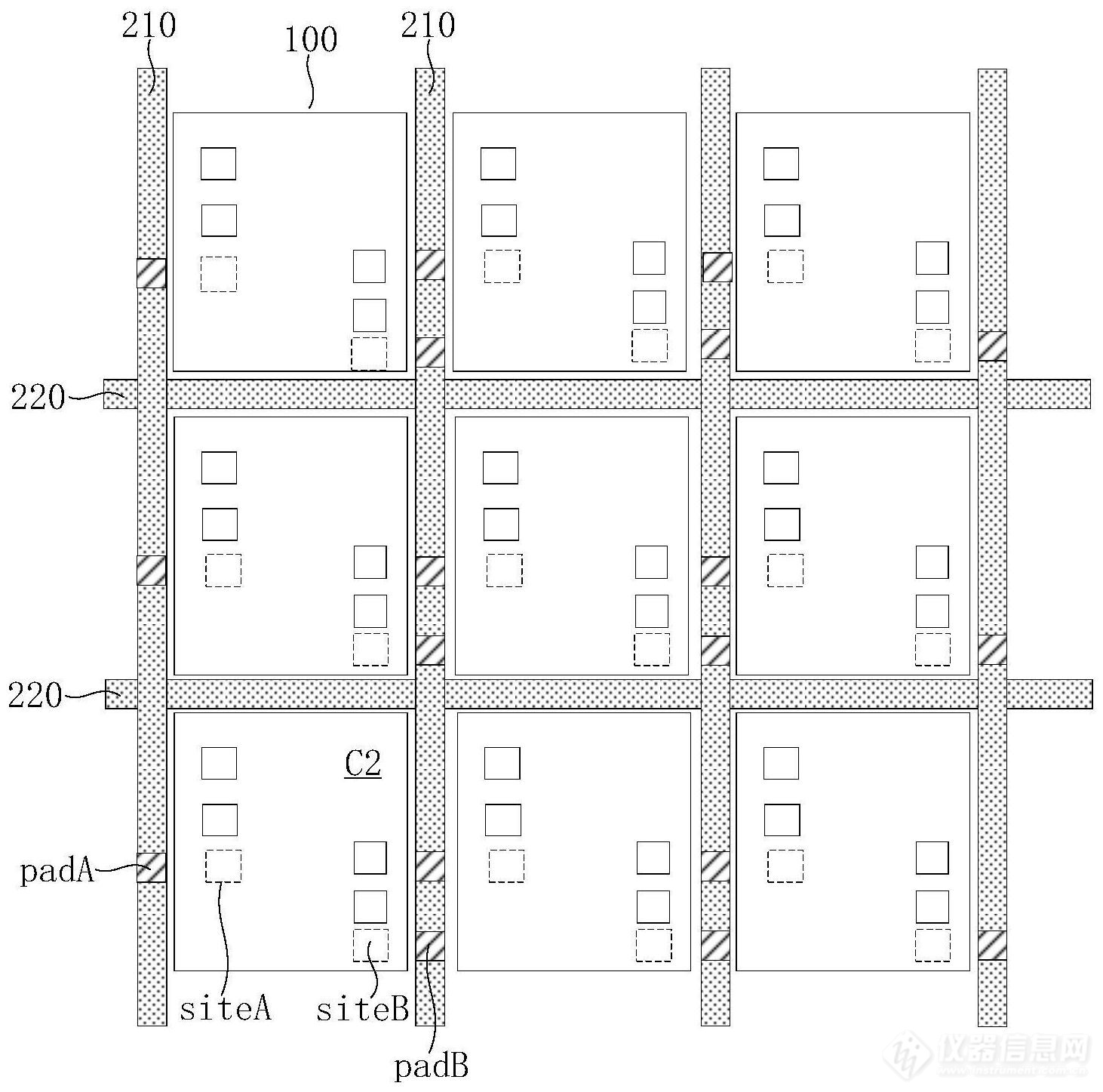

本申请涉及晶圆测试领域,具体涉及一种用于晶圆芯片并行测试的模拟量测试焊盘排布结构。所述晶圆包括若干个呈阵列式分布芯片,相邻芯片之间形成划片槽;相邻两列芯片之间形成纵向划片槽,相邻两排芯片之间形成横向划片槽;位于各个所述芯片周围的划片槽中,设有模拟量测试焊盘,所述模拟量测试焊盘与对应芯片电性耦合。本申请通过将模拟量测试焊盘设于对应芯片周围的划片槽中,在节省焊盘占用芯片面积的同时,通过保证在进行晶圆测试时所述模拟量测试焊盘与对应芯片电性耦合,即能够保证在晶圆芯片模拟参数并行测试的过程正常进行。

来源于:仪器信息网

热门评论

最新资讯

新闻专题

更多推荐