半导体情报,科学家在WSe₂场效应晶体管取得突破性成果!

导读:本文首次成功实现了基于n型和p型WSe₂场效应晶体管的两层CMOS芯片的M3D集成,展示了二维材料在推动M3D技术方面的巨大潜力。

【科学背景】

在过去六十年中,晶体管尺寸的不断缩小得益于诸如鳍式场效应晶体管(FET)技术的创新、高介电常数绝缘材料的集成、改进的互连技术以及极紫外光刻技术的进步。这些技术不断推动了集成电路(IC)组件密度的提升。然而,尽管器件级的缩放取得了显著进展,封装级的进展却相对滞后,这突显了三维(3D)集成作为一种“正交缩放”方法的重要性。3D集成通过减少占地面积、降低功耗、提高带宽、缩短连接布线以及降低寄生损耗等优点,提供了一种有前景的解决方案,能有效突破传统二维尺寸缩放的限制。

工业界目前主要采用铜微凸点和通过硅通孔(TSVs)来堆叠分别制造的芯片,但TSVs具有较大的占地面积,导致显著的寄生电容和热/机械应力。因此,单片3D(M3D)集成被认为是未来3D集成电路的关键技术,其通过在单个晶圆上顺序制造层间通孔,解决了TSVs带来的局限性。M3D集成实现了更高的垂直互连密度、更短的连线长度,从而提高了速度并降低了功耗,同时也允许在一个或多个层中集成非硅材料,以提升性能或丰富功能。然而,M3D集成在采用相同(非硅)半导体材料的互补FET方面仍处于探索阶段,这主要由于n型碳纳米管FET和p型二维FET的开发进展有限。

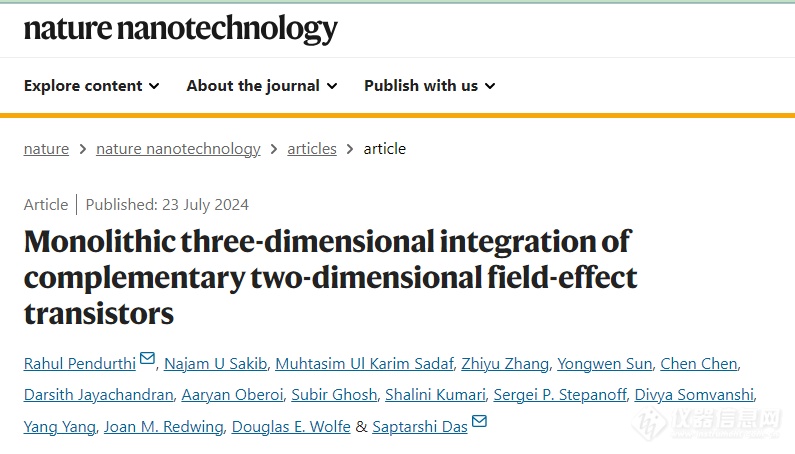

本研究针对这一现状,美国宾夕法尼亚州立大学Rahul Pendurthi,Saptarshi Das教授团队展示了基于n型和p型FET的两层互补金属氧化物半导体(CMOS)芯片的M3D集成。这些FET采用通过金属有机化学气相沉积(MOCVD)技术合成的大面积WSe₂制成。

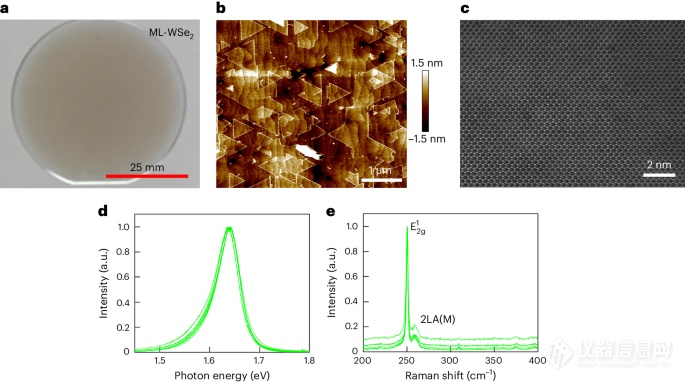

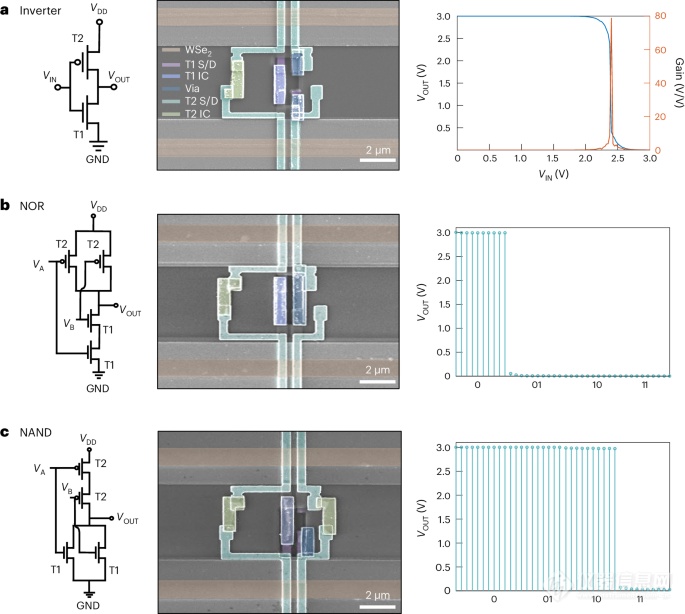

作者成功实现了晶体管级分区,将340个n型FET和340个p型FET分别放置在第1层和第2层。此外,作者展示了宽度为300 nm、间距为1 µm的密集层间通孔,这在封装技术中达到了先进水平。同时,作者成功实现了包括27个反相器、12个NAND门和12个NOR门在内的3D CMOS电路。通过在不超过200°C的温度下制造M3D CMOS堆叠,本研究为2D/Si混合技术的后端集成提供了兼容的解决方案。这些成果不仅突破了传统封装技术的限制,还展示了二维材料在推动M3D集成方面的巨大潜力。

【表征解读】

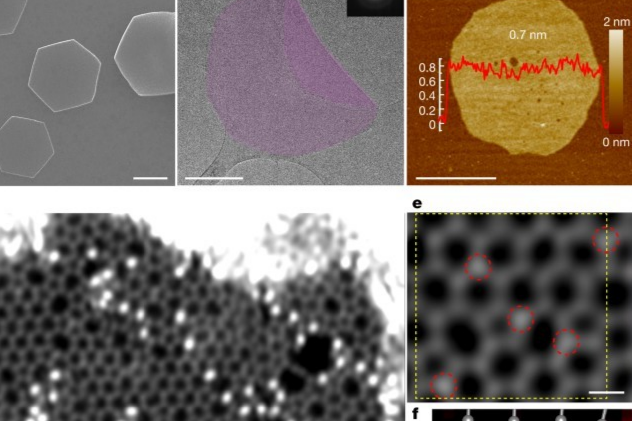

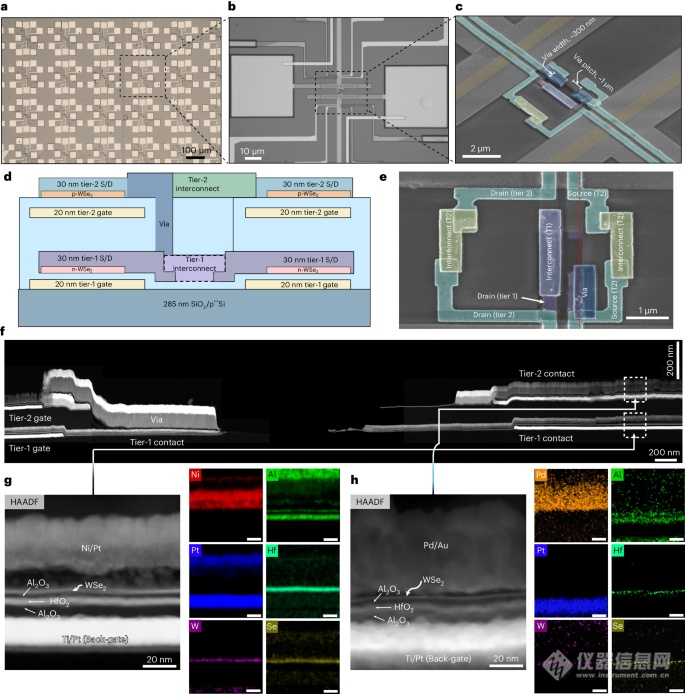

本文通过拉曼光谱和光致发光(PL)测试,揭示了多层WSe2薄膜的晶体结构和光学特性。这些表征手段使我们能够深入理解WSe2的电子性质及其在CMOS电路中的应用潜力。针对WSe2薄膜中观察到的光致发光现象,作者利用透射电子显微镜(TEM)对样品进行了微观结构分析,得到了层间耦合效应及其对电子迁移率的影响,进而挖掘了WSe2在高效电子器件中的应用价值。

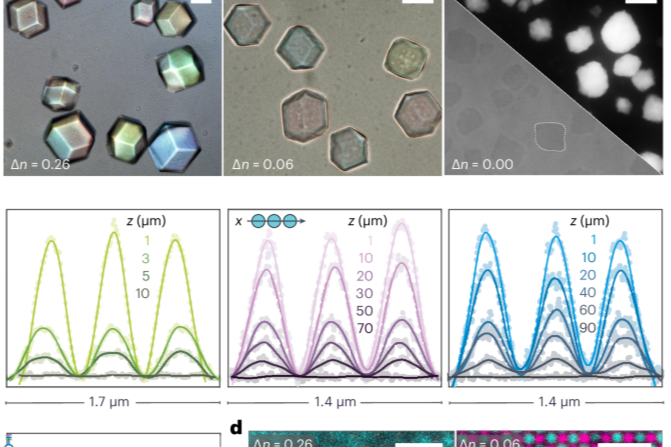

在此基础上,通过扫描电子显微镜(SEM)和聚焦离子束(FIB)技术,本文获得了二维材料的详细形貌和结构特征。这些表征结果表明,WSe2在微米尺度下展现出良好的均匀性和层间一致性,进一步证明了其在集成电路中作为半导体材料的可靠性。特别是在对比不同厚度的WSe2样品时,作者发现其电学性能和光学响应显著依赖于层数,这为设计新型器件提供了重要指导。

总之,经过综合的拉曼、PL、TEM和SEM等表征手段,深入分析了WSe2的结构特性和电子特性,进而制备出新型二维材料。这些研究不仅推动了对WSe2在集成电路中应用的理解,也为发展更高效的电子器件奠定了基础,标志着二维材料领域的又一重要进展。通过这些手段的结合,我们能够系统地解析材料的性能,并为未来的研究指明方向。

【科学图文】

图1:互补金属氧化物半导体CMOS 硒化钨WSe2 场效应晶体管FET的单片三维集成M3D。

图2:大面积有机金属化学气相沉积法MOCVD WSe2合成和3D叠层制造。

图3:单片三维集成M3D 互补金属氧化物半导体CMOS WSe2 场效应晶体管FET。

图4:单片三维集成M3D逻辑门。

【科学结论】

本文首次成功实现了基于n型和p型WSe₂场效应晶体管的两层CMOS芯片的M3D集成,展示了二维材料在推动M3D技术方面的巨大潜力。这种集成方式突破了传统二维缩放的限制,为器件集成密度的提升和性能的优化提供了新的解决方案。其次,通过采用300 nm宽、间距为1 µm的密集层间通孔,本研究实现了在两层芯片中连接超过340个n型FET和340个p型FET,标志着在高密度集成领域的显著进展。这种高密度的垂直互连方式不仅有效减少了互连线的长度,还降低了功耗和寄生损耗,提高了整体电路的性能。

此外,本研究在200°C以下的温度下成功制造了3D CMOS电路,包括27个反相器、12个NAND门和12个NOR门,展示了M3D CMOS技术在实际应用中的可行性。这一成果表明,M3D技术不仅可以解决传统二维缩放中的热处理和性能问题,还为2D/Si混合技术的后端集成提供了兼容的解决方案。这些发现不仅扩展了M3D技术在高性能电子器件中的应用范围,还为未来在二维材料和3D集成技术方面的进一步研究奠定了基础。

原文详情:Pendurthi, R., Sakib, N.U., Sadaf, M.U.K. et al. Monolithic three-dimensional integration of complementary two-dimensional field-effect transistors. Nat. Nanotechnol. (2024). https://doi.org/10.1038/s41565-024-01705-2

来源于:仪器信息网

热门评论

最新资讯

新闻专题

更多推荐