推荐厂家

暂无

暂无

留言咨询

留言咨询

留言咨询

留言咨询

留言咨询

留言咨询

400-860-5168转5919

400-860-5168转5919

留言咨询

留言咨询

400-860-5168转5919

400-860-5168转5919

留言咨询

留言咨询

400-860-5168转5919

400-860-5168转5919

留言咨询

留言咨询

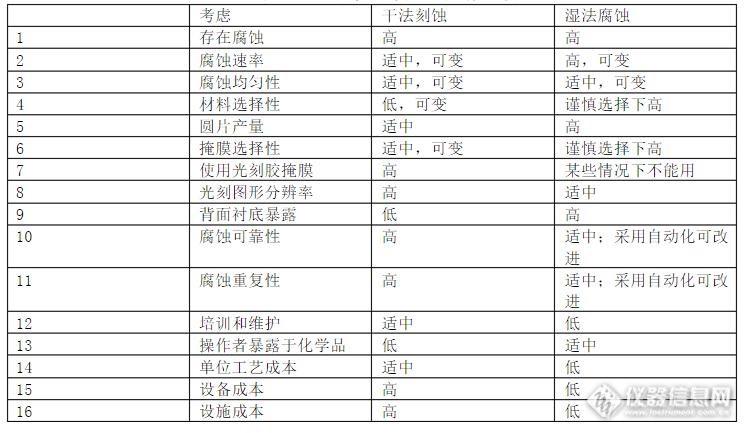

湿法腐蚀是使用液态腐蚀剂系统化的有目的性的移除材料,在光刻掩膜涂覆后(一个曝光和显影过的光刻胶)或者一个硬掩膜(一个光刻过的抗腐蚀材料)后紧接该步腐蚀。这个腐蚀步骤之后,通常采用去离子水漂洗和随后的掩膜材料的移除工艺。http://ng1.17img.cn/bbsfiles/images/2016/12/201612130959_01_3091062_3.jpg干法刻蚀的刻蚀剂是等离子体,是利用等离子体和表面薄膜反应,形成挥发性物质,或直接轰击薄膜表面使之被腐蚀的工艺。http://www.whchip.com/upload/201612/1481592347583553.jpg湿法腐蚀可替换工艺包括干法刻蚀,即使用一种或多种低压力的反应气体,采用RF感应激励后进行反应,然后再将反应生成的气态物质抽出;非等离子干法刻蚀,例如双氟化疝或氢氟酸的酸性蒸气腐蚀,拥有各向同性湿法腐蚀的诸多特性,该腐蚀通常在一个有限的腔室内完成。很少有微机械化或集成化的器件是在没有进行一些湿法化学处理的情况下开发或制造的。不管器件是否是电气的,机械的,电子的,集成的,光学的,光电子学的,生物的,聚合的,微流控的传感器或执行器,有关这些器件的制造工艺或过程的替换决定将对最终的技术和商业成功有重要影响。这些器件通常在硅衬底、化合物半导体、玻璃、石英、陶瓷或塑性材料上制造,可能涉及在这些材料上淀积一层或多层薄膜并光刻和腐蚀。这些层和淀积顺序受工艺和用于开发和制造该器件的工艺单元限制,随着层数的增长变的越来越复杂和相互影响。 近乎所有IC,MEMS,MOEMS,MST和NEMS类的器件的产生都很可能与一些湿法腐蚀工艺有关。整个工艺流程可被描述为一系列步骤或者序列,这些湿法腐蚀常用于选择性的去除淀积薄膜的一部分,剥去诸如硬掩膜和光刻胶等特定的材料,为以后的加工清洗和准备衬底,去除牺牲层和部分衬底,以及形成三维结构。一个湿法腐蚀工序需要考虑如下一些因素,包括有效的腐蚀剂,腐蚀选择性,腐蚀速率,各向同性腐蚀,材料的兼容性,工艺的兼容性,花费,设备的可用性,操作人员的安全,技术支持和适当的废物处理。干法刻蚀能实现各向异性刻蚀,保证细小图形转移后的高保真性。器件设计者,工艺设计师,或者制造商在工艺允许的情况下可能偏向使用一个完整的干法处理流程,但是许多标准的处理步骤例如光刻胶的显影和圆片清洗仍然湿法的。与干法刻蚀相比,湿法腐蚀工序在成本,速度,性能发面更有优势。干法刻蚀的仿真还不可用,如常用的微结构的选择性钻蚀或与晶向相关的腐蚀仿真等。考虑到干法刻蚀要求在一个昂贵的等离子区或者RIE腐蚀系统里有长的腐蚀时间,湿法腐蚀变得特别有吸引力,需要同时处理整盒圆片(25片装圆片盒)或更多的圆片时,湿法腐蚀在成本和时间上的效益更突出。 不管选择干法还是湿法加工工艺,总是强烈受到在特定的加工环境下设备的可用性及对开发者有用的工艺限制。成功的设计者,开发者和制造商几乎总是使用或修改趁手的工艺。除非是必须开发新工艺,安装新设备,或者取得新的工艺技能,一般总是避免额外的需求。理解什么时候要应用干法和湿法这两个工艺并且在可能的情况下使用标准工艺是很重要的。下表总结比较湿法和干法刻蚀之间的一般注意事项。 http://ng1.17img.cn/bbsfiles/images/2016/12/201612130959_02_3091062_3.jpg

光刻工艺光刻是用光刻胶、掩模和紫外光进行微制造 ,工艺如下 :(a)仔细地将基片洗净;(b)在干净的基片表面镀上一层阻挡层 ,例如铬、二氧化硅、氮化硅等;(c) 再用甩胶机在阻挡层上均匀地甩上一层几百 A厚的光敏材料——光刻胶。光刻胶的实际厚度与它的粘度有关 ,并与甩胶机的旋转速度的平方根成反比;(d) 在光掩模上制备所需的通道图案。将光掩模复盖在基片上,用紫外光照射涂有光刻胶的基片,光刻胶发生光化学反应;(e)用光刻胶配套显影液通过显影的化学方法除去经曝光的光刻胶。这样,可用制版的方法将底片上的二维几何图形精确地复制到光刻胶层上;(f) 烘干后 ,利用未曝光的光刻胶的保护作用 ,采用化学腐蚀的方法在阻挡层上精确腐蚀出底片上平面二维图形。掩模制备用光刻的方法加工微流控芯片时 ,必须首先制造光刻掩模。对掩模有如下要求:a.掩模的图形区和非图形区对光线的吸收或透射的反差要尽量大;b.掩模的缺陷如针孔、断条、桥连、脏点和线条的凹凸等要尽量少;c.掩模的图形精度要高。通常用于大规模集成电路的光刻掩模材料有涂有光胶的镀铬玻璃板或石英板。用计算机制图系统将掩模图形转化为数据文件,再通过专用接口电路控制图形发生器中的爆光光源、可变光阑、工作台和镜头,在掩模材料上刻出所需的图形。但由于设备昂贵,国内一般科研单位需通过外协解决,延迟了研究周期。由于微流控芯片的分辨率远低于大规模集成电路的要求,近来有报道使用简单的方法和设备制备掩模,用微机通过CAD软件将设计微通道的结构图转化为图象文件后,用高分辨率的打印机将图象打印到透明薄膜上,此透明薄膜可作为光刻用的掩模,基本能满足微流控分析芯片对掩模的要求。湿法刻蚀在光刻过的基片上可通过湿刻和干刻等方法将阻挡层上的平面二维图形加工成具有一定深度的立体结构。近年来,使用湿法刻蚀微细加工的报道较多,适用于硅、玻璃和石英等可被化学试剂腐蚀的基片。已广泛地用于电泳和色谱分离。湿法刻蚀的程序为 :(a) 利用阻挡层的保护作用,使用适当的蚀刻剂在基片上刻蚀所需的通道 ;(b) 刻蚀结束后 ,除去光胶和阻挡层,即可在基片上得到所需构型的微通道;(c)在基片的适当位置(一般为微通道的端头处)打孔,作为试剂、试样及缓冲液蓄池。刻有微通道的基片和相同材质的盖片清洗后,在适当的条件下键合在一起就得到微流控分析芯片。玻璃和石英湿法刻蚀时,只有含氢氟酸的蚀刻剂可用,如HF/HNO3,HF/ NH4。由于刻蚀发生在暴露的玻璃表面上,因此,通道刻的越深,通道二壁的不平行度越大 ,导至通道上宽下窄。这一现象限制了用湿法在玻璃上刻蚀高深宽比的通道。等离子体刻蚀等离子体刻蚀是一种以化学反应为主的干法刻蚀工艺,刻蚀气体分子在高频电场作用下,产生等离子体。等离子体中的游离基化学性质十分活泼,利用它和被刻蚀材料之间的化学反应,达到刻蚀微流控芯片的目的。等离子体刻蚀已应用于玻璃、石英和硅材料上加工微流控芯片 , 如石英毛细管电泳和色谱微芯片。先在石英基片上涂上一层正光胶 (爆光后脱落的光胶),低温烘干后,放置好掩模,用紫外光照射后显影,在光胶上会产生微结构的图象。然后用活性CHF3等离子体刻蚀石英基片 ,基片上无光胶处会产生一定的深度通道或微结构。这样可产生高深宽比的微结构。近来,也有将等离子体刻蚀用于加工聚合物上的微通道的报道。http://www.whchip.com/upload/201610/1477271936108203.jpg

作者:泛林集团 Semiverse Solutions 部门软件应用工程师 Pradeep Nanja介绍半导体行业一直专注于使用先进的刻蚀设备和技术来实现图形的微缩与先进技术的开发。随着半导体器件尺寸缩减、工艺复杂程度提升,制造工艺中刻蚀工艺波动的影响将变得明显。刻蚀终点探测用于确定刻蚀工艺是否完成、且没有剩余材料可供刻蚀。这类终点探测有助于最大限度地减少刻蚀速率波动的影响。刻蚀终点探测需要在刻蚀工艺中进行传感器和计量学测量。当出现特定的传感器测量结果或阈值时,可指示刻蚀设备停止刻蚀操作。如果已无材料可供刻蚀,底层材料(甚至整个器件或晶圆)就会遭受损坏,从而极大影响良率[1],因此可靠的终点探测在刻蚀工艺中十分重要。半导体行业需要可以在刻蚀工艺中为工艺监测和控制提供关键信息的测量设备。目前,为了提升良率,晶圆刻蚀工艺使用独立测量设备和原位(内置)传感器测量。相比独立测量,原位测量可对刻蚀相关工艺(如刻蚀终点探测)进行实时监测和控制。使用 SEMulator3D工艺步骤进行刻蚀终点探测通过构建一系列包含虚拟刻蚀步骤、变量、流程和循环的“虚拟”工艺,可使用 SEMulator3D 模拟原位刻蚀终点探测。流程循环用于在固定时间内重复工艺步骤,加强工艺流程控制(如自动工艺控制)的灵活性[2]。为模拟控制流程,可使用 "For Loop" 或 "Until Loop"(就像计算机编程)设置一定数量的循环。在刻蚀终点探测中,可使用 "Until Loop",因为它满足“已无材料可供刻蚀”的条件。在循环中,用户可以在循环索引的帮助下确认完成的循环数量。此外,SEMulator3D 能进行“虚拟测量”,帮助追踪并实时更新刻蚀工艺循环中的材料厚度。通过结合虚拟测量薄膜厚度估测和流程循环索引,用户可以在每个循环后准确获取原位材料刻蚀深度的测量结果。用 SEMulator3D 模拟刻蚀终点探测的示例初始设定在一个简单示例中,我们的布局图像显示处于密集区的四个鳍片和密集区右侧的隔离区(见图1)。我们想测量隔离区的材料完成刻蚀时密集区的刻蚀深度。我们将用于建模的区域用蓝框显示,其中有四个鳍片(红色显示)需要制造。此外,我们框出了黄色和绿色的测量区域,将在其中分别测量隔离区的薄膜厚度 (MEA_ISO_FT) 和沟槽区的刻蚀深度 (MEA_TRENCH_FT)。工艺流程的第一步是使用 20nm 厚的硅晶体层(红色)、30nm 的氧化物(浅蓝色)和 10nm 的光刻胶(紫色)进行晶圆设定(图2)。我们曝光鳍片图形,并对使用基本模型刻蚀对光刻胶进行刻蚀,使用特定等离子体角度分布的可视性刻蚀对氧化物材料进行刻蚀。氧化物对光刻胶的选择比是100比1。我们在 SEMulator3D 中使用可视性刻蚀模型来观察隔离区和有鳍片的密集区之间是否有厚度上的差异。[img]https://img1.17img.cn/17img/images/202401/uepic/a41bec0f-535e-420a-8a19-ed4282cd5c66.jpg[/img]图1:模型边界区域(蓝色),其中包含四个鳍片(红色)和用于测量隔离区(黄色)和沟槽区(绿色)薄膜厚度的两个测量区域[img]https://img1.17img.cn/17img/images/202401/uepic/630f2367-a619-4bc9-8608-09c532bef68f.jpg[/img]图2:SEMulator3D 模型,硅晶体(红色)、氧化物(浅蓝色)和在光刻胶中显影的四个鳍片(紫色)SEMulator3D 刻蚀终点探测循环SEMulator3D 的工艺流程使用 Until Loop 循环流程。我们将测量隔离区的材料厚度,并在隔离氧化物薄膜耗尽、即厚度为0时 (MEA_ISO_FT==0) 停止该工艺。在这个循环中,每个循环我们每隔 1nm 对氧化物材料进行1秒的刻蚀,并同时测量此时隔离区氧化物薄膜厚度。此外,我们将在每次循环后追踪两个鳍片间沟槽区的刻蚀深度。这个循环索引有助于追踪刻蚀循环的重复次数(图3)。[img]https://img1.17img.cn/17img/images/202401/uepic/5041079a-7da3-459f-907c-f62f1b6ac8c1.jpg[/img]图3:SEMulator3D 刻蚀终点探测模拟中的循环流程结果对隔离薄膜进行刻蚀,直至其剩余 20nm、10nm 和 0nm 深度的模拟结果如图4所示。模型中计算出隔离薄膜厚度的测量结果,以及两个鳍片间沟槽区的刻蚀深度。[img]https://img1.17img.cn/17img/images/202401/uepic/b5d9d13c-68e2-4389-80d1-b974c07afe99.jpg[/img]图4:隔离区薄膜厚度剩余 20nm、10nm 和 0nm 的工艺模拟流程,及相应从光刻胶底部开始的沟槽刻蚀深度我们对循环模型进行近30次重复后,观察到隔离区的薄膜厚度已经达到0,并能追踪到沟槽区氧化物的刻蚀深度(当隔离区被完全刻蚀时,密集区 30nm 的氧化物已被刻蚀 28.4nm)。结论SEMulator3D 可用来创建刻蚀终点探测工艺的虚拟模型。这项技术可用来确定哪些材料在刻蚀工艺中被完全去除,也可测量刻蚀后剩下的材料(取决于刻蚀类型)。使用这一方法可成功模拟原位刻蚀深度控制。使用类似方法,也可以进行其他类型的自动工艺控制,例如深度反应离子刻蚀 (DRIE) 或高密度等离子体化学[url=https://insevent.instrument.com.cn/t/Mp][color=#3333ff]气相[/color][/url]沉积 (HDP-CVD) 工艺控制。参考资料:[1] Derbyshire, Katherine. In Situ Metrology for Real-Time Process Control, Semiconductor Online, 10 July 1998, https://www.semiconductoronline.com/doc/in-situ-metrology-for-real-time-process-contr-0001.[2] SEMulator3D V10 Documentation: Sequences, Loops, Variables, etc.[来源:大半导体产业网][align=right][/align]