一、连接时没有引线的无引线键合

尽管引线键合采用自动化,但它是一个非常耗时的过程。材料成本也是一个挑战,因此无引线连接技术备受关注。

什么是 TAB?

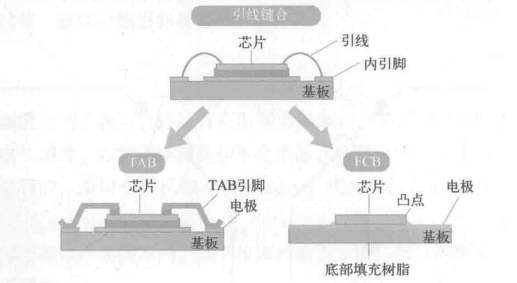

不使用金线连接芯片电极(Pad)和封装基板的方法称为无引线键合(WirelessBonding)。无引线键合大致分为两种。一种是载带焊(TapeAutomatedBonding,TAB),另一种是倒装焊(FipChipBonding,FCB)。下图显示了与引线键合相比的两种方法之间的差异。

无引线键合比较

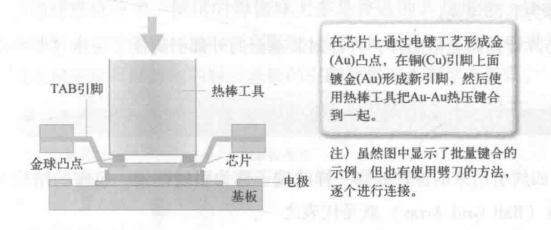

首先关于TAB,如下图所示,使用一种称为热棒工具(Hot Bar Tool)的夹具,把划片后芯片的A1焊盘(带金凸点)与TAB引脚(内引脚)进行热黏合TAB引脚其实是在聚酰亚胺胶带开口处放置的Cu引脚上镀金而成。这些TAB引线有规则地排列在聚酰亚胺胶带上,以卷轴的形式存放,这是TAB的独有特色。这些TAB引脚比金引线更粗。

TAB的流程

近来芯片的引脚数量越来越多,连接面积越来越大,因此批量焊接的精度很难保证为此也有一种新方法,可以使用劈刀逐个进行连接。

什么是 FCB?

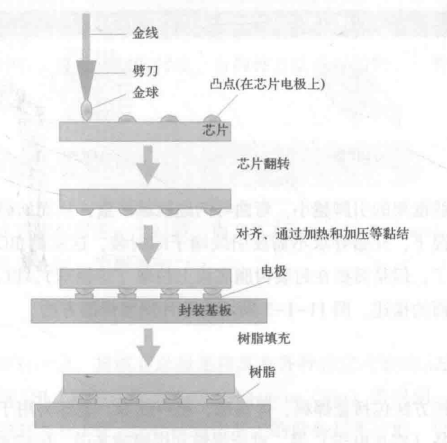

接下来,我们将讨论倒装焊(FCB)。如下图所示,将金引线键合方法应用于芯片的凸点(Bump)安装位置,在芯片电极上形成金球凸点。把准备倒装焊。的芯片翻转一下成为“脸朝下”的状态,与高性能LSI专用的多层布线封装基板的电极对齐,然后加热连接。此方法称为金球凸点。之后,注人树脂以填满芯片与封装基板之间的间隙,称为底部填充。之后在芯片背面贴上散热片,并在封装基板的外部引脚挂上锡球。

FCB的流程

二、无须引线框架的BGA

LSI芯片四周引出来的像蜈蚣脚一样的端子称为引线框架。也有的结构不需要这种引线框架,BGA(BallGridArray)就是代表之一。

没有引线框架的意义是什么?

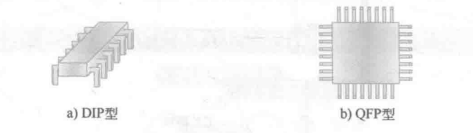

无论是前段制程还是后段制程,微细化的趋势不可阻挡。随着LSI向高集成度、高性能不断迈进,引脚数量不断增加。下图显示了引线框架类型的封装示例。举例来说使用QFP,这种引线框架类型的封装,最大引脚数为476针端子,间距为0.4mm,这已经是极限了。而且引线框架在切筋时使用的刀片,其刀片厚度约为0.1mm,刀片的精度和模具的精度也都达到了极限。

引线框架类型的封装示例

另一方面,引线框架的引脚越小,弯曲等问题就越严重,从而妨碍了后面在线路板上的安装。在这种情况下,开始寻求不需要引线端子的封装,这就是BGA类型的封装。虽然不需要引线端子了,但是需要在封装树脂底板上植球(焊锡球),以及分割封装的工序这些请参阅本节后面的描述。FCB所示为芯片倒装焊的方法。

什么是植球?

倒装芯片的连接方法包括金焊料、焊锡球、超声波等,金焊料用于窄间距产品,焊锡球用于高可靠性产品(汽车电子)等。对金焊料和焊锡球来说,低成本、微细化的要求也越来越高。

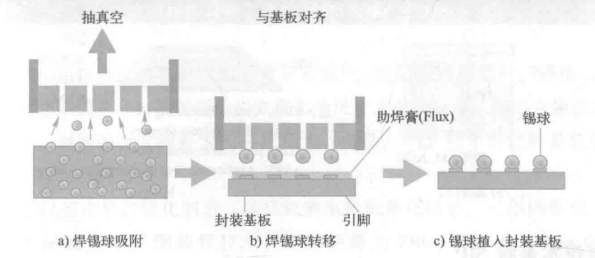

本节介绍焊锡球形成技术,使用的焊锡球大多是普通的共晶焊料。如下图所示,使用焊锡球吸附夹具对焊锡球进行真空吸附,该夹具将封装引脚的位置与装有焊锡球的槽对齐,通过在预先涂有助焊剂的封装基板的引脚位置植入锡球来实现。

植入锡球的 BGA 封装

此外,还有一种方法可以将焊料通过丝网印刷到指定位置,然后用热回流来生成锡球。

通常,以封装基板的框架为单位进行运输。与引线框架类型的封装一样,使用托架来容纳框架。形成锡球后,进行切割的封装。有两种方法进行切割,一种是单独切割,另一种是批量切割。

三、旨在实现多功能的SiP

通常,一颗LSI芯片被封进一个封装,而SiP(SysteminPackage)是将具有各种各样功能的多颗ISI芯片封在同一个封装中。

什么是 SiP?

您可能对 SiP略有印象,其核心思想是将具有各种特定功能的LSI封到一个封装中而不是将单一的系统LSI(通常也称为SoC,System on Chip)集成到一个芯片中。如果我们要在一个芯片上制造系统LSI,没有精细化加工的设备是不行的,设计也极其复杂。可是,电路设计也好,制造工艺也罢,反正是将已经验证过的芯片组合到一起,封装到一个管壳中,那一定更快捷。

例如在功能不断发展的手机系统LSI中,这种想法值得考虑。手机需要应用的融合(例如支持0ne-Seg和互联网),并且产品周期很短,可以考虑通过单一封装来应对以上需求,开发类似堆积木结构的 SiP 比开发新的LSI更快。

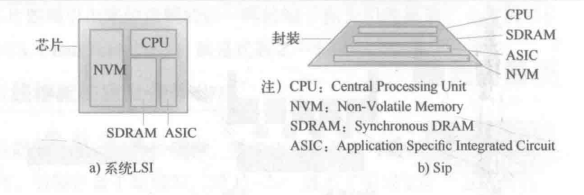

手机中需要的高端LSI在国内制造,低端LSI在国外制造,也在如此进行。下图显示了SiP与系统LSI的比较。

SoC与SiP的比较示意图

从封装技术来看 SiP

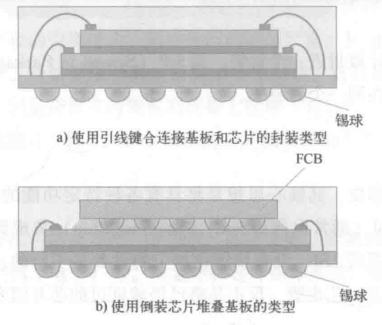

从技术上讲,SiP实际封装有两种类型:通过引线键合的芯片叠层封装,以及充分利用倒装焊技术的三维封装(3D封装)。下图举例说明了使用引线键合连接基板和芯片的封装类型,以及使用倒装芯片堆叠基板的类型。这些SiP有望提供新的“系统解决方案”,此外,使用之前介绍的TSV(Through Silicon Via)的三维实现,为SiP的发展提供了更大的可能。TSV也是不使用引线键合的方法。

堆叠芯片封装示例

四、真实芯片尺寸的晶圆级封装

晶圆在被切割成单个LSI芯片之前,以晶圆的状态进行封装,这就是晶圆级封装(WLP)。它不仅适用于半导体,同样适用于MEMS等什么是晶圆级封装?

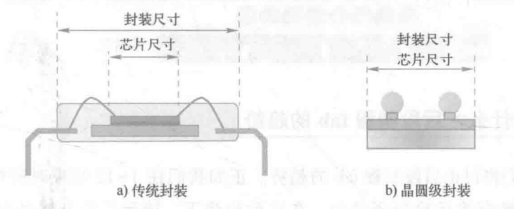

晶圆级封装是指在晶圆原有状态下重新布线,然后用树脂密封,再植入锡球引脚最后划片将其切割成芯片,从而制造出真实芯片尺寸大小的封装。把芯片装进封装中的时候,无论如何,封装的尺寸都要大于芯片尺寸。可是,WLP技术的优势是能够实现几乎与芯片尺寸一样大小的封装。

此外,不仅芯片是批量化制造,而且封装也是批量化制造,可以降低成本。这种封装方法在技术层面采用了倒装焊技术,所以被称为FBGA(意思是FipChip类型的BGA)。芯片也称为晶圆级CSP(Chip Size Package)。下图比较了它与传统封装之间的不同。

与传统封装的比较

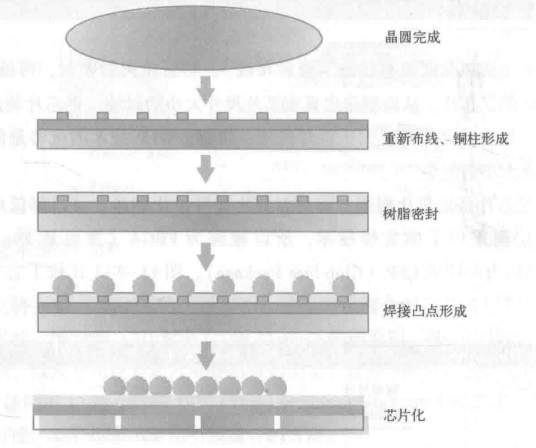

晶圆级封装的流程

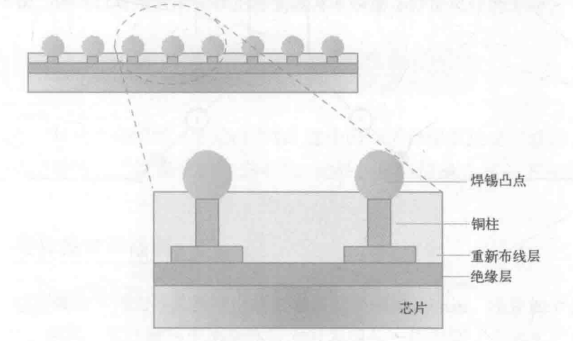

晶圆级封装工艺流程如下图所示。首先进行再布线工程,主要包括形成重新布线层的层间绝缘膜,称为中间介质层(Interposer);接下来形成通孔和重新布线层(RDL,Re-Distribute Layer),用来连接芯片和外部端子;接下来形成铜柱(Post,使用铜等材料).然后在铜柱上面生成凸点(Bump)。接下来的步骤是用树脂密封,再形成焊球并用划片机切割成所需的芯片。

晶圆级封装工艺流程

下图显示了一个放大的视图。在切割之前,可以在晶圆状态下进行测试。

晶圆级封装的放大视图

OSAT 是什么?后段制程fab 的趋势

最后,我们将讨论后段制程fab的趋势。越来越多的半导体制造商将后段制程外包。在这种趋势下,接受后段制程外包的制造商称为OSAT(0utsourced Semiconductor Assembly And Test),我们称其为外包半导体封装测试工厂,与外包了前段制程的代工厂是类似的性质。OSAT不仅增强了传统的低端封装,还强化了本章中所介绍的具有高附加值的高端封装技术。可以说,这是因为智能手机所引领的半导体产品占据的阵地不断扩大而导致的结果。在一些代工厂中,有整合后段制程的趋势,这一领域无论在商业上还是技术上都备受关注。在日本,像J-DEVICE公司这样的OSAT诞生了,它是把半导体制造商的后段制程部门整合到一起了,在整合后段制程的同时,水平分工也正在取得进展。

参考文献:

内容来源:爱蛙科技编辑整理

半导体 | 离子注入设备

半导体 | 清洗和干燥设备

半导体 | 半导体工艺的发展趋势

半导体 | 前道工艺概述

相关产品

关注

拨打电话

留言咨询