派恩杰“集成ESD的SiC功率MOSFET器件及制备方法”专利获授权

导读:派恩杰半导体获得专利,开发出集成ESD防护的SiC功率MOSFET器件,旨在保护芯片免受静电损害,提高器件可靠性与安全性,同时优化成本与集成度。

天眼查显示,派恩杰半导体(杭州)有限公司近日取得一项名为“集成ESD的SiC功率MOSFET器件及制备方法”的专利,授权公告号为CN112951922B,授权公告日为2024年7月23日,申请日为2021年3月25日。

背景技术

半导体领域,静电释放(ESD)会对芯片中的器件,特别是对于MOSFET器件这种极薄栅介质的器件,产生破坏作用,在栅极产生一个高电场,使得栅介质在高电场下发生绝缘击穿,从而使器件失效。静电保护是指当带有静电的物体或人体接触芯片时能够迅速消除静电产生的电压或电流,达到保护芯片器件的目的。在各种可靠性测试标准中都有静电(ESD)的标准,因此静电保护也是器件设计中一项重要指标。

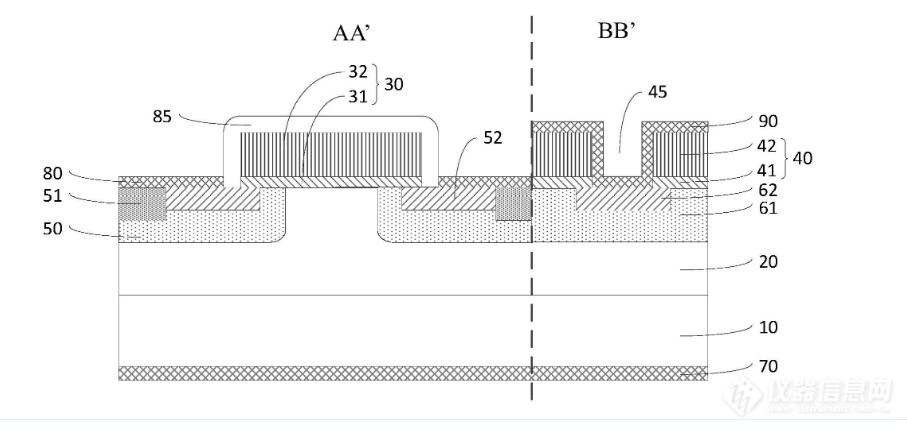

在现有的硅基的MOSFET和IGBT器件中,利用二极管作为集成ESD是很常见的设计,请参考图1,MOSFET器件M1的栅极和源极之间连接有一个二极管D1,当静电释放在MOSFET器件M1的栅极产生一个高电场,在栅介质被高电场下作用下发生绝缘击穿之前,优先击穿了二极管D1的PN结,使得MOSFET器件M1的栅极免于被击穿,从而达到保护芯片器件的目的。

但现有的硅基的MOSFET和IGBT器件中,由于硅基的PN结二极管的击穿电压很低,所以硅基的ESD二极管通常设置在栅极的多晶硅中,采用N型和P型掺杂多晶硅得到二极管。但这种方法不仅需要额外的光刻版,增加了产品的成本,且由于是在栅极的多晶硅中集成二极管,也会影响MOSFET和IGBT的栅氧特性。

发明内容

本发明提供了一种集成ESD的SiC功率MOSFET器件及其制备方法,由于用于ESD的PN结二极管是集成在MOSFET器件本身需要的栅极压焊区下方,不需要额外的芯片面积,不会影响芯片的集成度。且栅极压焊区的面积较大,使得PN结二极管的面积也可以较大,PN结二极管环绕在栅极压焊区的下方,可以利用栅极压焊区的面积,增大PN结二极管的面积提高ESD泄放能力;由于通过调节PN结边缘的形貌和掺杂浓度就可以调节PN结二极管的击穿电压,因此通过在第一掺杂离子重注入区和第二掺杂离子注入区的边缘设置多个尖峰角,就可以调节PN结二极管的击穿电压;且所述PN结二极管的形成是和形成MOSFET器件的工艺步骤同步进行,不额外增加光刻掩膜步骤,不会增加芯片制作成本。

来源于:仪器信息网

热门评论

最新资讯

新闻专题

更多推荐