半导体情报,科学家提出室温下的氧化铟三维垂直集成新方法!

导读:本文探索并实现了在室温下将氧化铟(In2O3)薄膜晶体管(TFT)单片式三维集成的方法,这一创新不仅突破了传统集成电路制造的温度限制,还展示了可与互补金属氧化物半导体(CMOS)工艺兼容的技术路线。

【科学背景】

三维垂直集成技术是当今集成电路领域的研究热点,通过在单一衬底上堆叠多层器件,可以实现高密度、能效高且低成本的集成电路。然而,开发可扩展的三维薄膜晶体管(TFT)集成工艺面临诸多挑战。传统的制造方法如晶片-晶片结合存在低功率密度、高温处理及缺乏标准化等问题,限制了其广泛应用。

为了克服这些挑战,沙特阿卜杜拉国王科技大学Saravanan Yuvaraja,Xiaohang Li等人合作在“Nature Electronics”期刊上发表了题为“Three-dimensional integrated metal-oxide transistors”的研究论文。科学家们提出了在室温下在硅/二氧化硅衬底上单片式三维集成氧化铟(In2O3)TFT的方法。这种方法与互补金属氧化物半导体(CMOS)工艺兼容,能够堆叠多达十层的n型通道In2O3 TFT,并制造不同结构的器件,包括底栅、顶栅和双栅TFT。

研究结果显示,双栅器件表现出优异的电性能,如最大场效迁移率达到15 cm2 V−1 s−1,亚阈摆幅为0.4 V dec−1,开关比高达108。通过在不同位置单片集成双栅In2O3 TFT,科学家们还成功创建了具有高信号增益和良好噪声裕度的单极反相器电路。尽管在本研究中尚未制造垂直互连访问,但提出了潜在的制造方法,有望减少制造复杂性。这一研究为三维集成电路技术的发展提供了新的思路和解决方案,推动了在低成本、高效能集成电路领域的进一步探索与应用。

【科学亮点】

(1)实验首次在室温下实现了单片式三维垂直集成的氧化铟(In2O3)薄膜晶体管(TFT),采用了与互补金属氧化物半导体(CMOS)工艺兼容的方法。

(2)实验通过堆叠十层n型通道的In2O3 TFT,在不同层次制造了底栅、顶栅和双栅TFT,展示了多种结构的器件。作者的研究结果表明,双栅TFT器件在电性能上表现出显著的提升,包括最高达到15 cm2 V−1 s−1的场效迁移率、0.4 V dec−1的亚阈摆幅和高达108的开关比。

(3)通过在不同位置单片集成双栅In2O3 TFT,作者成功创建了具有约50的信号增益和优良噪声裕度的单极反相器电路。这些双栅器件还允许微调反相器,以实现对称的电压传输特性和最佳的噪声裕度。

【科学图文】

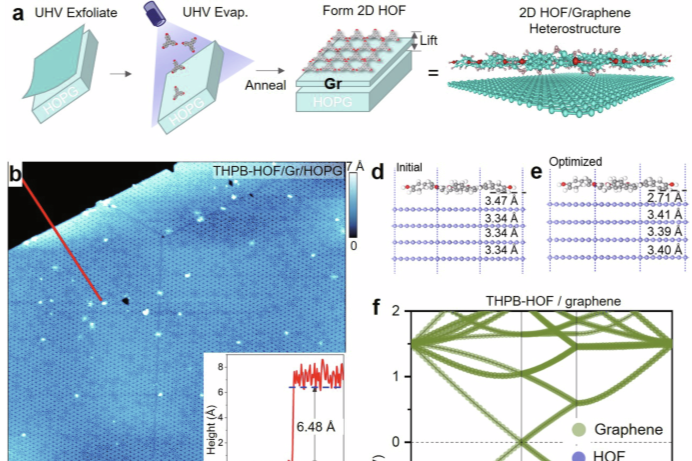

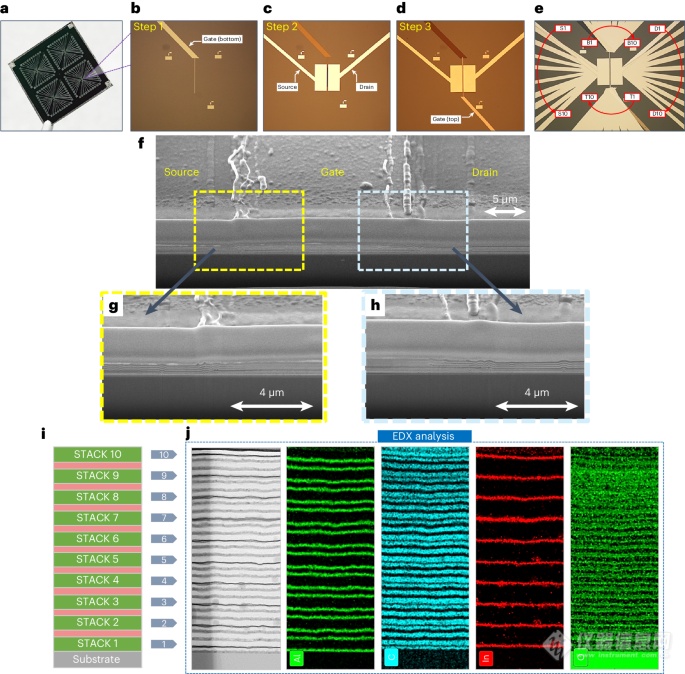

图1: 氧化铟In2O3薄膜晶体管thin-film transistor,TFT的3D单片集成。

图2. 制造垂直集成在10-S器件中的单个薄膜晶体管TFT的工艺步骤及其结构和元素分析。

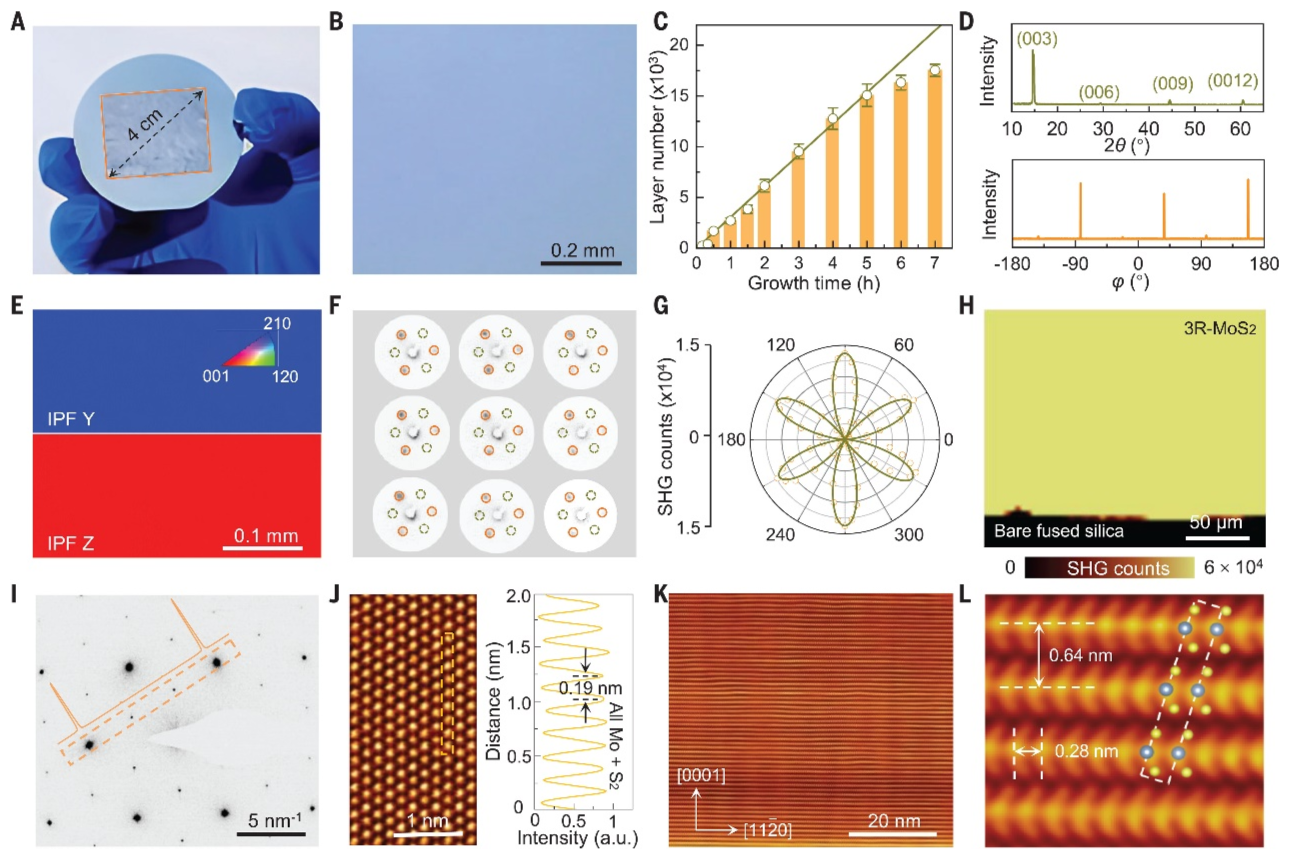

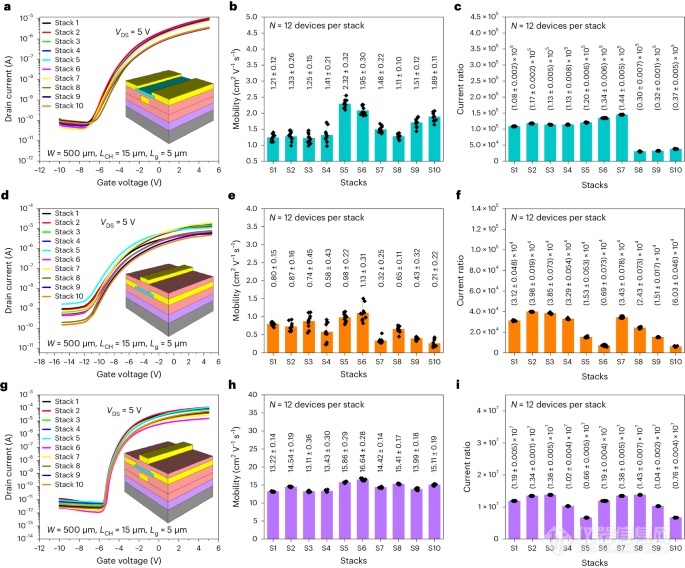

图3. 器件特性。

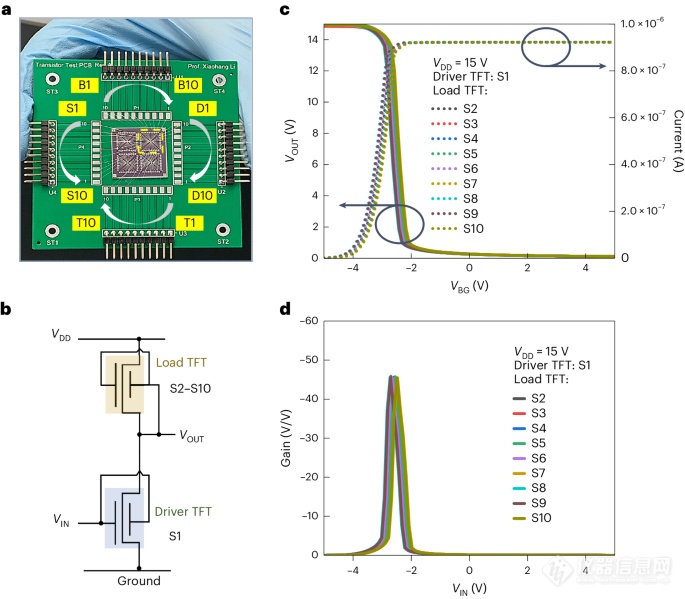

图4. 使用垂直集成的In2O3 薄膜晶体管TFT制造的电压反相器电路和操作特性。

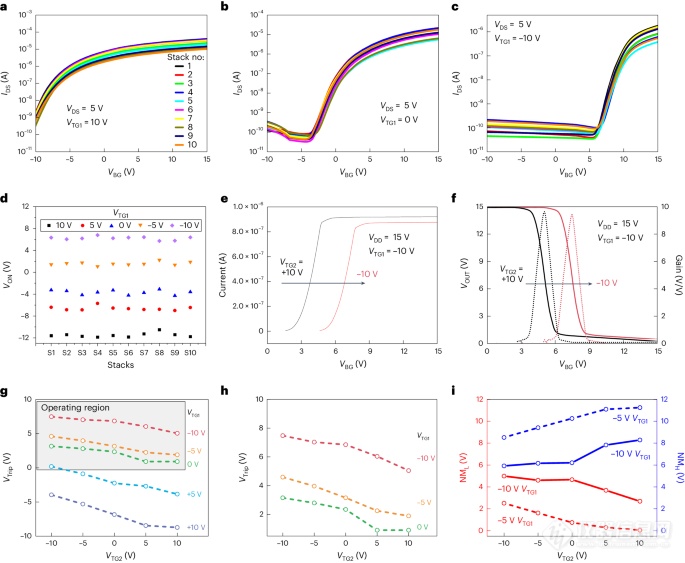

图5. 可配置反相器电路的特性图。

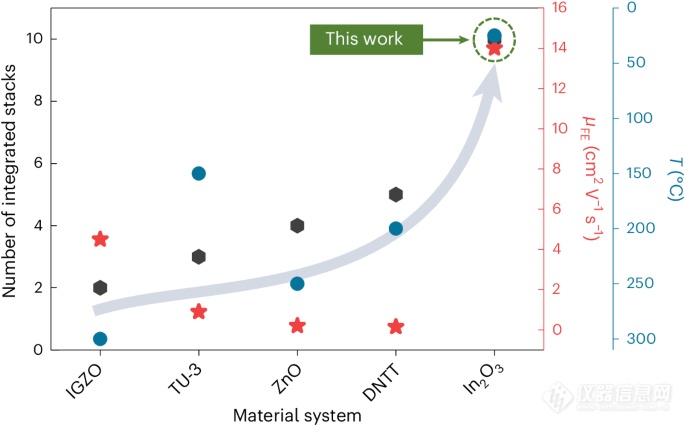

图6. 基准图表。

【科学结论】

本文探索并实现了在室温下将氧化铟(In2O3)薄膜晶体管(TFT)单片式三维集成的方法,这一创新不仅突破了传统集成电路制造的温度限制,还展示了可与互补金属氧化物半导体(CMOS)工艺兼容的技术路线。

通过这一方法,研究团队成功在硅/二氧化硅(Si/SiO2)衬底上堆叠了多达十层的In2O3 TFTs,实现了各种不同结构的设计。实验结果显示,这些器件具有优异的电性能,包括高达15 cm2 V−1 s−1的场效迁移率、仅为0.4 V dec−1的亚阈摆幅以及高达108的开关比,为未来高密度、能效高且低成本的集成电路提供了新的可能性。

特别值得关注的是,通过在不同层次单片集成双栅In2O3 TFT,研究团队成功创建了性能优越的单极反相器电路,展示了高达50的信号增益和优异的噪声裕度。这不仅突显了三维垂直集成技术在电子器件设计中的潜力,还为实现更复杂、功能更强大的集成电路奠定了基础。

参考文献:Yuvaraja, S., Faber, H., Kumar, M. et al. Three-dimensional integrated metal-oxide transistors. Nat Electron (2024). https://doi.org/10.1038/s41928-024-01205-0

来源于:仪器信息网

热门评论

最新资讯

新闻专题

更多推荐