推荐厂家

暂无

暂无

留言咨询

留言咨询

留言咨询

留言咨询

留言咨询

留言咨询

据新华社伦敦5月19日电 英国研究人员最近报告说,他们研发出一种基于“电阻性记忆体”的新型存储设备,与现在广泛使用的闪存相比,耗电量更低,而存取速度要快上一百倍。 电阻性记忆体的基础是忆阻材料,这种材料的特殊性在于,在外加电压时其电阻会发生变化,随后即使取消外加电压,它也能“记住”这个电阻值。在此基础上开发出的存储设备与现有闪存相比更快更节能,是业界近来的研发热点。但以前开发出的这种存储设备只能在高度真空环境中运行。 英国伦敦大学学院等机构研究人员日前在《应用物理学杂志》上报告说,他们发现可用硅的氧化物制作一种新的忆阻材料,相应存储设备可在常规环境下运行,因此应用价值大大提高。 研究人员安东尼·凯尼恩说,这种新型存储设备的能耗只有闪存的约千分之一,而其存取速度是闪存的一百倍以上。 据介绍,这项成果与科学史上许多发现一样都是源于意外。研究人员最开始是在用硅氧化物制作发光二极管,但在实验过程中出了故障,发现所用材料的电学性质变得不稳定了,检查之后发现它们电阻在变化,原因是已经变成了忆阻材料,于是正好把它们转用于研发新型存储设备。(记者 黄堃)

田园、山村、老牛、老人、稻田、白鹅、绿树,和找虫子吃的一对公鸡与母鸡[img]http://ng1.17img.cn/bbsfiles/images/2007/09/200709250016_64838_1627905_3.jpg[/img]

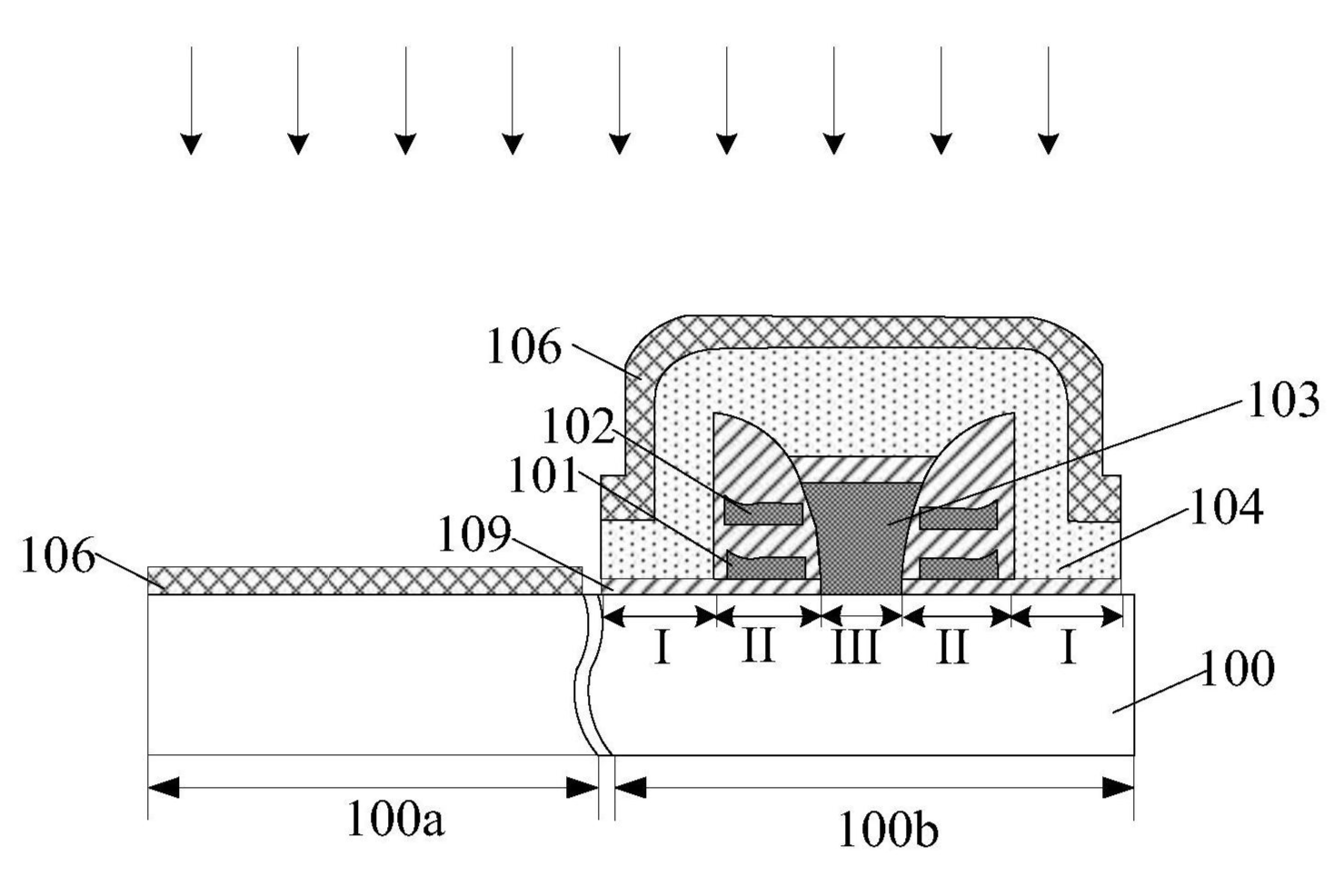

12月15日报道,台湾“国研院”纳米(台称:“奈米”)组件实验室领先全球,开发出全球最小的9纳米功能性电阻式内存(R-RAM)数组晶胞;这个新内存在几乎不需耗电的情况下,1平方厘米面积内可储存1个图书馆的文字数据,将让信息电子产品的轻薄短小化有无限发挥的可能性,这项技术预计在5到10年内进入量产。 台湾“国研院”院长陈文华,以及负责“9纳米超节能内存”开发的何家骅博士14日召开记者会,公布这项重大研究成果。 何家骅指出,随着可携式3C产品对体积越来越小以及容量越来越大的需求日益增加,如何能研发出体积更小、记忆量更大的内存,是全球研究人员努力的目标。 如今台湾开发出最小的9纳米功能性电阻式内存(R-RAM)数组晶胞,容量比现比的闪存增大20倍,但耗电量却降低了200倍,应用这个技术在1平方厘米面积下,可以储存1个图书馆的文字数据,而且可再借立体堆栈设计,进一步提升容量,让信息电子产品的轻薄短小化有无限发挥的可能性。 这项重要开发成果已于12月8日在美国旧金山举行的国际电子组件会议(IEDM)正式发表,引起国际微电子产学研界高度重视。 何家骅预料,这项新技术5到10年内量产,届时将可对全球新台币1兆元的传统闪存产生重大贡献,也希望这项技术能在2025年时有机会协助台湾于全球闪存的市场占有率提升至10%以上的产值。