华羿微电“一种低栅极电荷屏蔽栅MOSFET器件及其制作方法”专利获授权

导读:华羿微电子获专利,开发低栅极电荷屏蔽栅MOSFET,优化高频特性与开关损耗,适用于中高压领域,显著提升性价比。

天眼查显示,华羿微电子股份有限公司近日取得一项名为“一种低栅极电荷屏蔽栅MOSFET器件及其制作方法”的专利,授权公告号为CN117476770B,授权公告日为2024年7月19日,申请日为2023年11月16日。

背景技术

沟槽型功率MOS器件能够在节省器件面积的同时得到较低的通态电阻,因此具有较低的导通损耗,已经在中低压应用领域全面取代平面式功率MOS器件。但是采用密集而精细的沟槽栅后,由于沟道面积的增加导致栅极电荷增大,从而影响到器件的高频特性和开关损耗。特别是随着产品应用领域朝着薄,轻,小方向发展,要达到上述目的,就需要提升整个系统的开关频率,这样就导致普通的沟槽型功率MOS器件在开关特性的缺点表现的越来越明显,如何提高器件的开关速度和开关损耗以适应节能以及高频应用的需求具有十分重要的意义。

造成开关损耗大和开关速度慢的主要原因是由于沟槽型功率MOS器件在栅-源之间和栅-漏之间存在有较大的寄生电容,即栅-源电容Cgs和栅-漏电容Cgd。功率MOS管在开和关两种状态转换时,Cgd的电压变化远大于Cgs上的电压变化,相应的充、放电量Qgd较大,所以Qgd对开关速度的影响较大。如华虹NEC在中国专利(专利申请号:200510026546.5)中提出了厚底栅氧技术(Thick Bottom Oxide),从而达到降低Cgd的目的。但是该技术的不足在于Cgd只能降低约30%,仍不能满足节能以及高频应用的需求。因此,如何进一步显著的降低栅漏寄生电容,而不影响器件导通电阻,从而大大提高沟槽型功率MOS器件的高频特性和降低开关损耗成为本技术领域人员的努力方向。而基于电荷平衡原理的SGT(屏蔽栅型)MOSFET器件在很大程度上改变了动态特性和导通电阻之间的关系,使得器件FOM值更低(将导通电阻(Rdson)和栅电荷(Qg)的乘积最优值(FOM)作为评价器件性价比的标准)。

发明内容

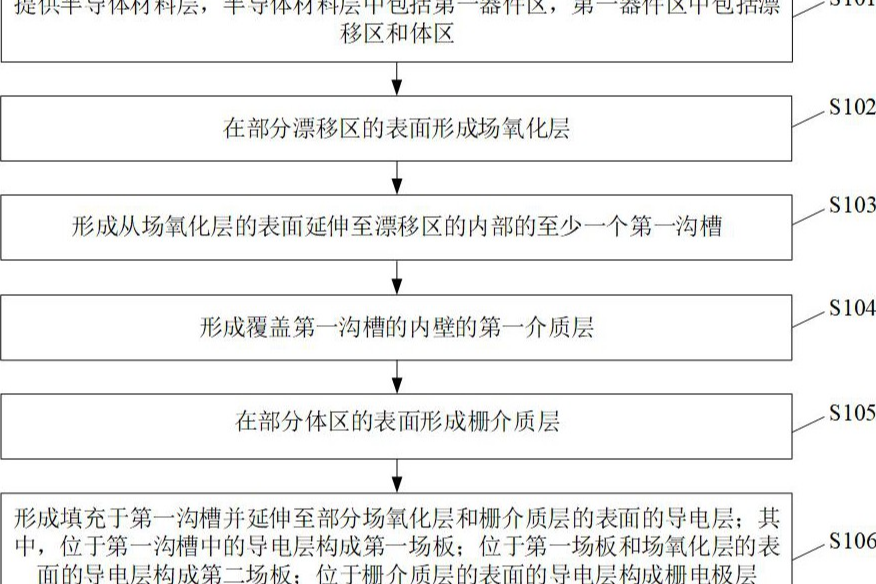

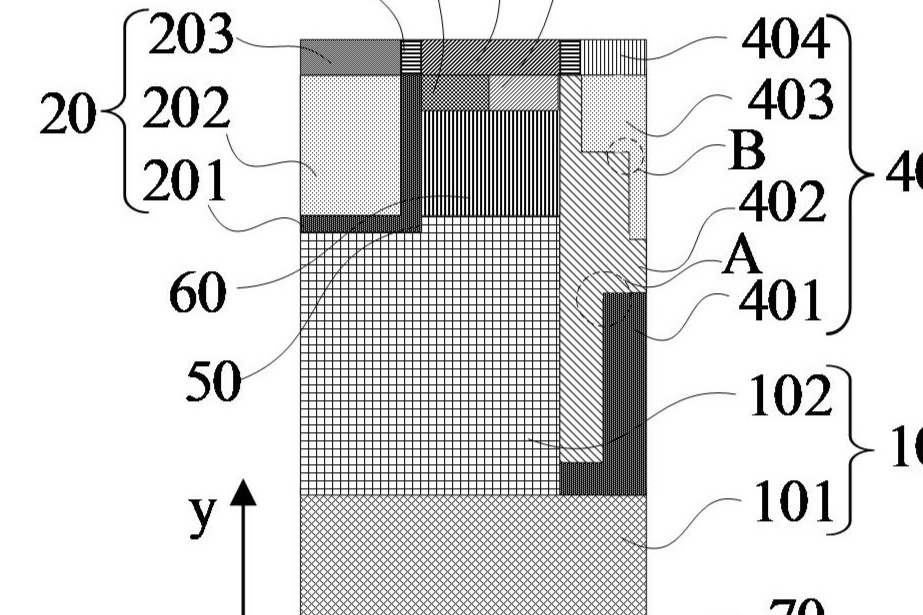

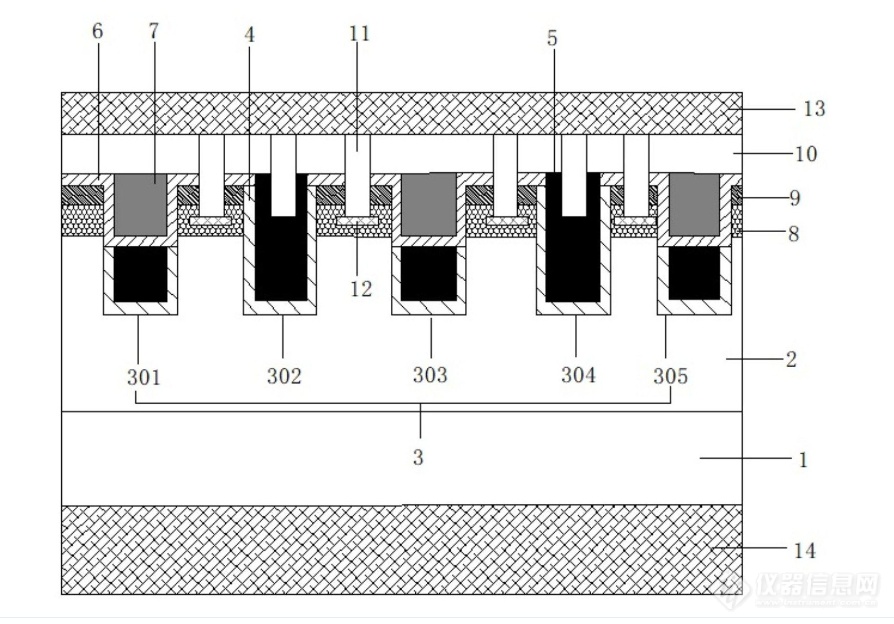

本发明公开了一种低栅极电荷屏蔽栅MOSFET器件及其制作方法,将器件有源区部分沟槽区域的源极多晶硅或者栅极多晶硅通过接触孔与源极金属层相连,使得该部分区域不参与整个器件的导通,能够有效降低器件的栅极电荷,同时由于沟槽下方屏蔽栅的存在可以保障器件有足够击穿电压。该器件在中高压领域具有极大优势,当器件有源区50%的区域采用此种技术将使得器件的FOM最优值降低~46.5%(以150V耐压器件为例),从而最终使得器件最优值FOM降低并且拥有更高的性价比。该器件的制作方法能够很好的与现有屏蔽栅型MOSFET器件制造工艺兼容,因此不会带来不可实现工艺的技术瓶颈,具有很高的转化价值。

来源于:仪器信息网

热门评论

最新资讯

新闻专题

更多推荐