仪器情报,科学家提出高密度垂直晶体管制备表征新技术!

导读:本文通过创新的T形层压方法,成功克服了传统横向制造工艺与垂直结构的不兼容性,为高密度垂直侧壁晶体管的制造开辟了新途径。传统上,晶体管的制造依赖于平面处理技术,而垂直方向的器件堆叠则面临着工艺复杂度和低

【科学背景】

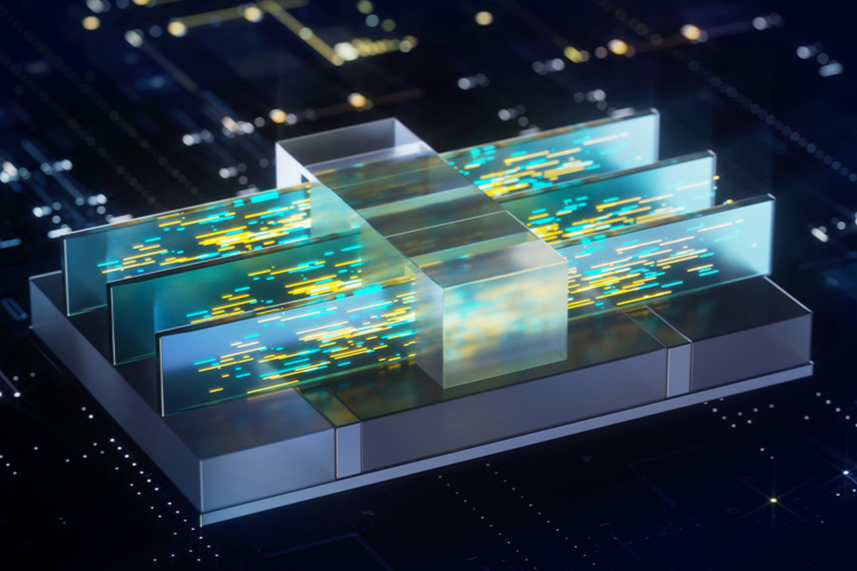

垂直晶体管(VFET)是一种源极和漏极垂直对齐,电流垂直流过晶圆表面的晶体管架构。近年来,随着技术的发展和对高密度集成电路需求的增加,垂直晶体管因其能够在不增加芯片面积的情况下实现高密度堆叠的特点,成为了研究热点。然而,实现高密度垂直晶体管具有相当大的挑战,主要归因于垂直结构与传统横向制造工艺的不兼容性。具体来说,传统的平面工艺使用的物理粒子如光子、反应离子或物理/化学气相,只能在晶圆平面内生成多个结构,而无法在垂直方向上进行大规模制造。此外,制造垂直晶体管需要复杂的多层沉积和图案化步骤,这使得工艺复杂且产量低。

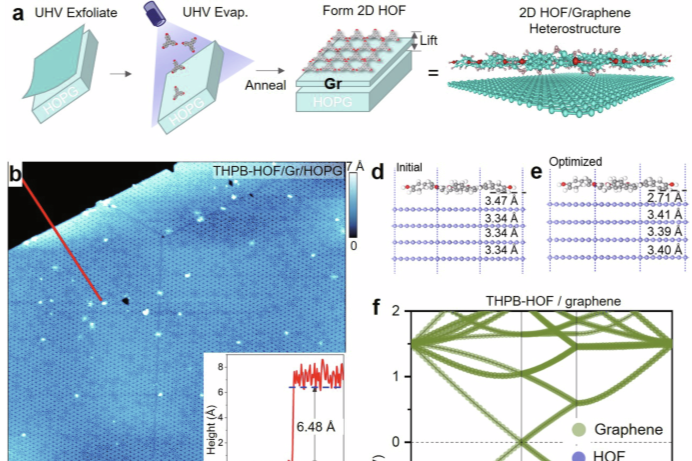

有鉴于此,湖南大学邹旭明、刘渊、廖蕾教授以及美国加利福尼亚大学圣迭戈分校物理系Chunhui Rita Du教授合作在“Nature Communications”期刊上发表了题为“High-density vertical sidewall MoS2 transistors through T-shape vertical lamination”的最新论文。科学家们提出了一种通过T形层压方法实现高密度垂直侧壁晶体管的新方法。这种方法的核心是先在平面基板上预制横向晶体管,然后使用定制设计的T形印章将其干释放并层压到垂直基板上。这一技术克服了平面工艺与垂直结构之间的不兼容性,使预制的晶体管可以在不损坏或退化的情况下与垂直基板完好接触。

通过这一技术,研究团队在0.035 μm²的小面积内垂直堆叠了60个MoS2晶体管,达到理论上的1.7 × 10¹¹ cm-2的器件密度。此外,他们还提出了两种可扩展制造垂直侧壁晶体管阵列的方法,包括同时在多个垂直基板上层压,以及在同一垂直基板上多周期逐层层压。研究结果表明,这种新方法为实现高密度垂直晶体管和垂直电子器件提供了一条有效的替代途径,开辟了高密度集成电路的新维度。

【科学亮点】

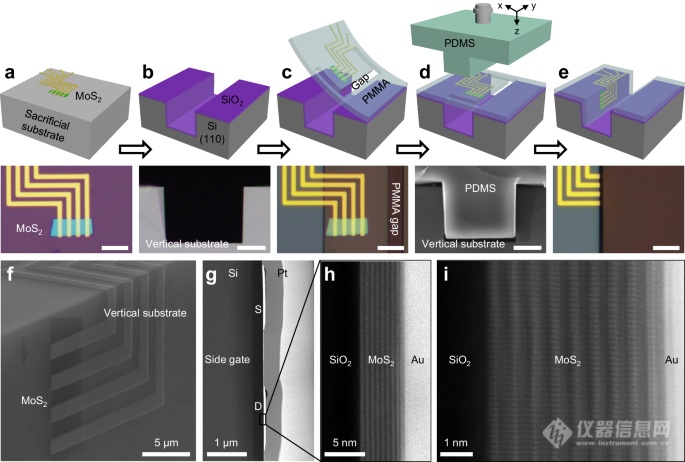

(1)实验首次使用T形层压方法,将预制的横向晶体管转移到垂直基板上,实现了高密度垂直侧壁晶体管。这一技术突破克服了传统平面工艺与垂直结构之间的不兼容性,使得横向晶体管可以在垂直基板上无损层压。

(2)实验通过以下几个关键步骤和结果,展示了这一技术的有效性和潜在应用:

步骤一:在平面基板上预制横向MoS2晶体管。通过常规批处理工艺制造横向晶体管,以确保其性能和质量。

步骤二:使用定制设计的T形PDMS印章进行层压。通过干层压技术,将预制的横向晶体管从平面基板转移到垂直基板上。干层压过程中产生的低应变确保了晶体管与垂直基板完好接触,无损坏或退化。

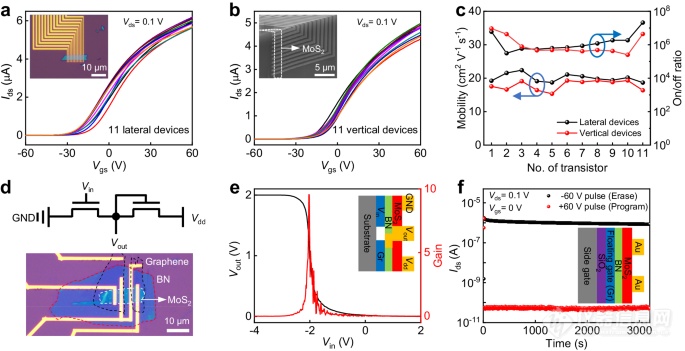

结果一:通过SEM、STEM和电气特性表征验证了层压后晶体管的完整性和功能性,证明了该方法的有效性。

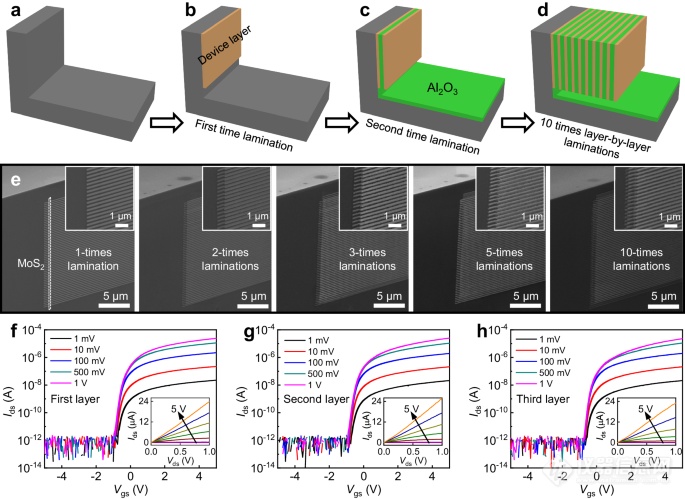

结果二:实现了在0.035 μm²的垂直面积内垂直堆叠60个MoS2晶体管,相应的理论器件密度达到了1.7 × 10¹¹ cm⁻²。实验展示了在小面积内实现高密度垂直器件堆叠的可能性。

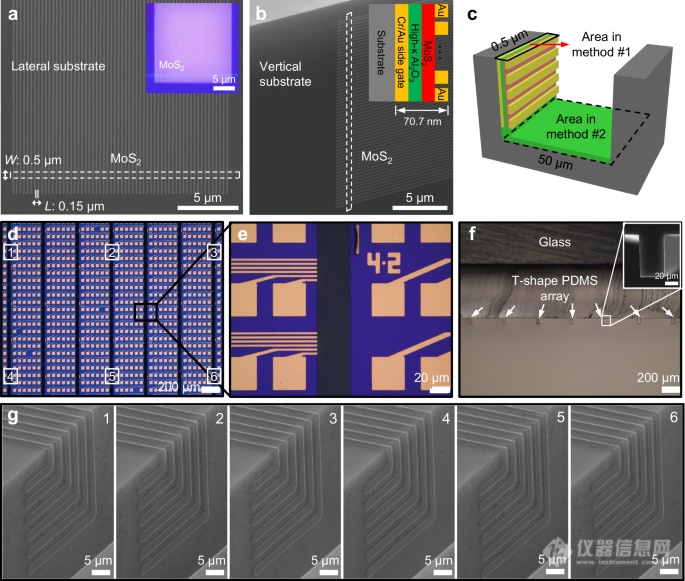

步骤三:提供了两种可扩展制造垂直侧壁晶体管阵列的方法:一是同时在多个垂直基板上进行层压,二是使用多周期逐层层压在同一垂直基板上进行堆叠。

结果三:展示了在不同基板上制造大规模垂直侧壁晶体管阵列的可行性,进一步拓展了这一技术的应用范围。

【科学图文】

图1:基于MoS2的垂直侧壁晶体管的垂直层压工艺和表征。

图2:MoS2晶体管的电气特性表征。

图3:可扩展的垂直侧壁晶体管制造。

图4:高密度垂直器件的逐层垂直集成。

【科学结论】

本文通过创新的T形层压方法,成功克服了传统横向制造工艺与垂直结构的不兼容性,为高密度垂直侧壁晶体管的制造开辟了新途径。传统上,晶体管的制造依赖于平面处理技术,而垂直方向的器件堆叠则面临着工艺复杂度和低产量的挑战。本文所提出的T形层压方法不仅保留了传统制造的高效性和成本效益,还在垂直方向上实现了多器件的紧密堆叠,大大提升了器件密度和集成度。

此外,本文的成功实验验证了干层压过程中的低应变特性,确保了晶体管与垂直基板的良好接触和稳定性,从而在器件性能和一致性上取得了显著的进展。这一技术创新不仅对垂直电子器件领域具有深远的影响,还为未来集成电路设计提供了新的思路和可能性。通过在小尺寸区域内成功堆叠多个MoS2晶体管,并展示出极高的器件密度,本文为实现更小型化、更高性能的电子设备奠定了坚实的实验基础。

原文详情:Tao, Q., Wu, R., Zou, X. et al. High-density vertical sidewall MoS2 transistors through T-shape vertical lamination. Nat Commun 15, 5774 (2024). https://doi.org/10.1038/s41467-024-50185-4

来源于:仪器信息网

热门评论

最新资讯

新闻专题

更多推荐