芯联集成“沟槽型功率器件结构及其制造方法”专利公布

导读:芯联集成电路制造股份有限公司研发新型沟槽型功率器件结构及制造方法,旨在提高对准精度,扩大接触孔与栅极沟槽间距,增加相邻栅极间发射极区面积,解决阈值电压开启难题。

天眼查显示,芯联集成电路制造股份有限公司“沟槽型功率器件结构及其制造方法”专利公布,申请公布日为2024年7月23日,申请公布号为CN118380411A。

背景技术

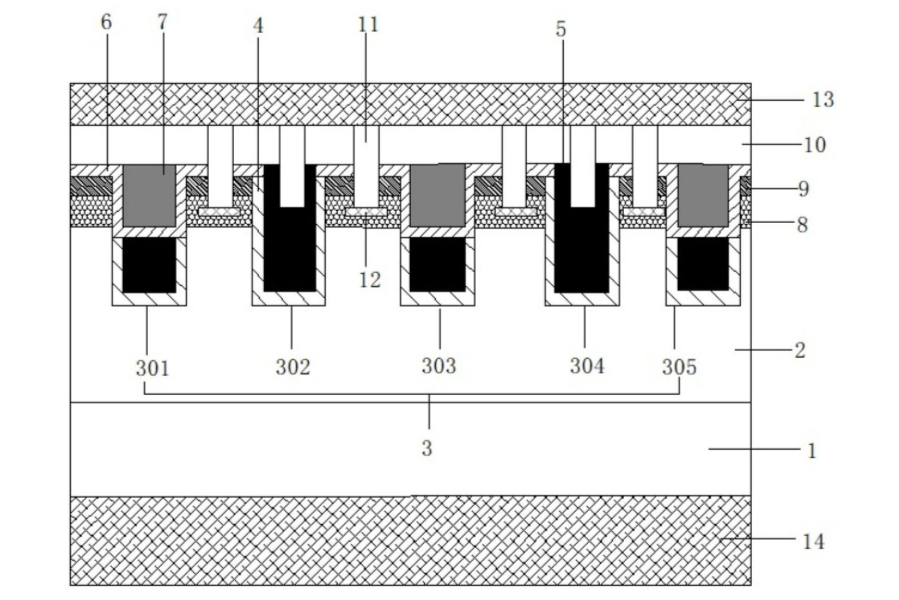

常规的沟槽型功率器件结构,例如,IGBT(Insulated Gate Bipolar Transistor,绝缘栅双极型晶体管)、Trench MOSFET (沟槽型金属氧化物晶体管)等,在制作接触孔时,由于设计规则和器件物理模型的限制,需要严格控制接触孔与栅极沟槽之间的对准精度,通常光刻机能力在50~100nm左右。

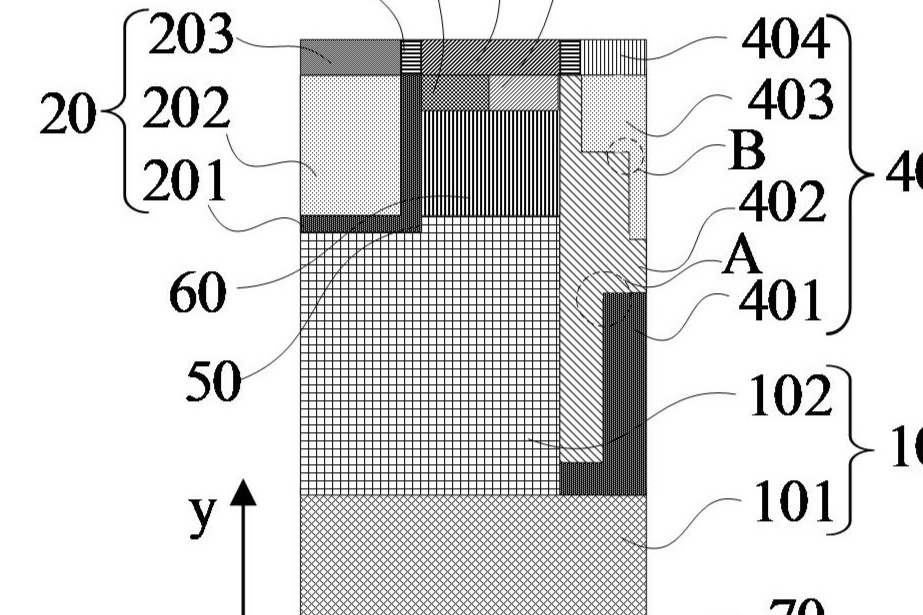

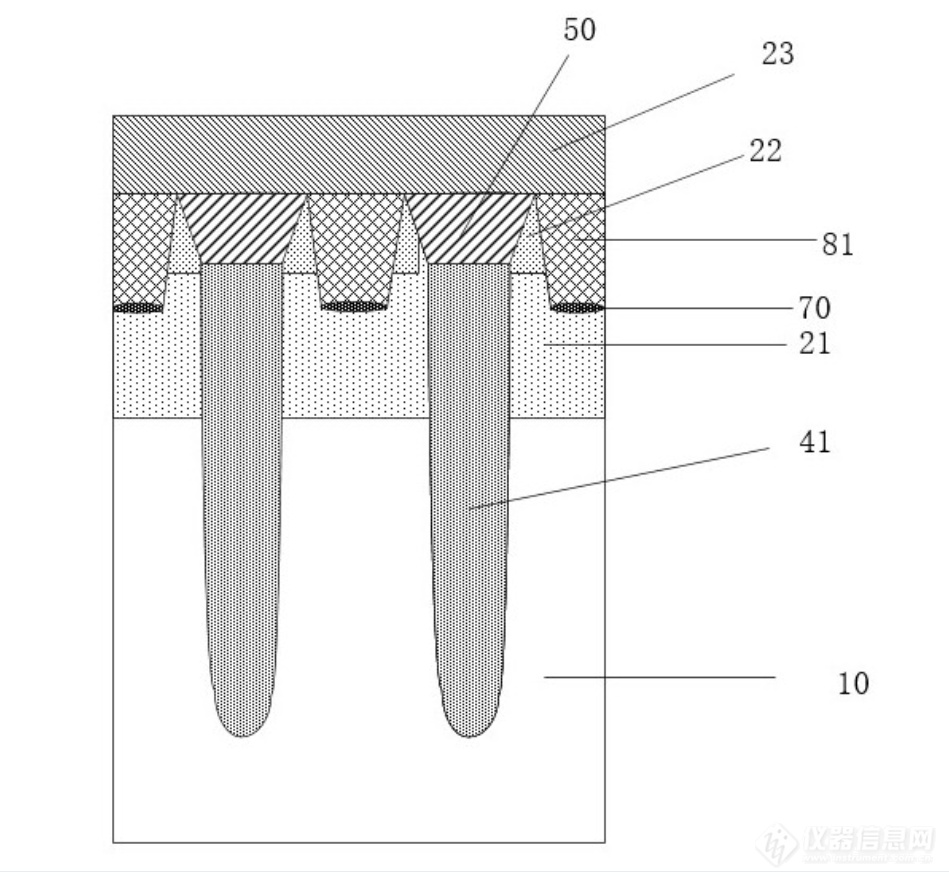

随着器件尺寸的不断缩小,器件单元间距也随之缩小,如图1所示,当器件单元间距(cell pitch)d缩小到1um左右时,接触孔200到沟槽100之间的自然间距已不足200nm,需求将对准精度限制在50nm以内,显然通常的光刻机无法保证对准精度,从而导致接触孔会发生偏移。接触孔200底部注入的杂质离子在一定的激活温度下向两侧横扩,接触孔200发生偏移导致两侧离子浓度不同而导致不能同时开启。另外,现有技术中,在接触孔200刻蚀完成之后,位于相邻沟槽之间的发射极区300的面积大幅减小,存在阈值电压正常开启困难的问题。

发明内容

本发明提供一种沟槽型功率器件结构及其制造方法,在半导体衬底内形成第一沟槽和自所述第一沟槽的底部向下延伸的第二沟槽,第一沟槽用于填充栅极,第二沟槽用于填充介质层,所述第一沟槽包括缩口区段,缩口区段从顶部至底部开口宽度逐渐减小,如此,可使得相邻栅极沟槽之间通过离子注入所形成的发射极区的面积增大,从而可以解决现有技术中因发射极区面积过小而影响阈值电压正常开启的问题。

来源于:仪器信息网

热门评论

最新资讯

新闻专题

更多推荐