推荐厂家

暂无

暂无

400-860-5168转2189

400-860-5168转2189

留言咨询

留言咨询

400-860-5168转0727

400-860-5168转0727

留言咨询

留言咨询

400-860-5168转6169

400-860-5168转6169

留言咨询

留言咨询

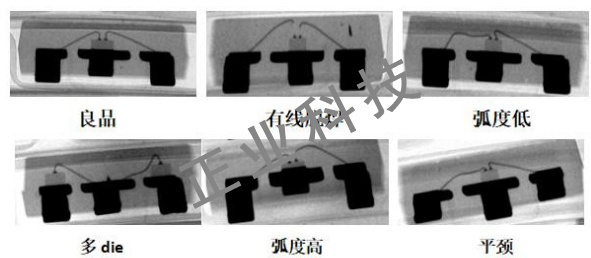

半导体芯片失效分析实验室汇总随着半导体技术的发展,芯片已经成为现代电子产品中不可缺少的部分。然而,芯片在长时间运行后可能会出现失效或故障,这将导致电子产品无法正常使用。为了解决这个问题,半导体芯片失效分析实验室应运而生。半导体芯片失效分析实验室是一种专门用于分析芯片故障原因和找出解决方案的实验室。它主要由多种设备和技术组成,包括光学显微镜、扫描电子显微镜、离子注入系统、穿透电子显微镜、电子束刻蚀机等。半导体芯片失效分析实验室可以用于以下方面的分析:1.失效分析如果芯片出现了故障,失效分析可以用来找出导致问题的原因。分析的过程通常包括对芯片进行非常规测试,如X射线衍射、扫描探针显微镜和热分析等,以找出故障根源,如堆积缺陷、擦除缺陷、漏电等。2.质量控制半导体芯片失效分析实验室也可以用于质量控制,以确保每个芯片都符合准确的规格和标准。质量控制分析通常包括对芯片进行成品检验,如外观检查、电性能测量和可靠性测试等。半导体芯片失效分析实验室汇总1.北京软件产品质量检测检验中心芯片失效分析实验室(简称:北软检测)成立于2002 年7月。北软芯片失效分析实验室可以进行全流程的失效分析,可靠性测试,安全验证等。主要包括点针工作站(Probe Station)、反应离子刻蚀(RIE)、微漏电侦测系统(EMMI)、X-Ray检测(2D X-ray,3D X-ray)、超声波扫描显微就(SAT)、缺陷切割观察系统(FIB系统)、体式显微镜、金相显微镜、研磨台(定点研磨,非定点研磨,封装研磨)、激光黑胶层取出系统(自动decap,laser decap)、自动曲线追踪仪(IV)、切割制样模块、扫描电镜(SEM)、能谱成分分析(EDX)、交变温湿度试验箱、高温储存试验、低温存储试验、温湿度存储试验等。通讯地址:北京市海淀区东北旺西路8号中关村软件园3A楼联系人:赵工?2.南京微电子技术研究所半导体芯片失效分析实验室南京微电子技术研究所半导体芯片失效分析实验室是国内最早成立的芯片失效分析实验室之一。实验室配备有先进的设备和技术,可对芯片的物理结构、器件参数、芯片性能、线路连接等方面进行全面的分析和测试。3.上海半导体研究所失效分析实验室上海半导体研究所失效分析实验室成立于2005年,是一家具备IC生产能力的高新技术企业。实验室在芯片失效分析领域积累了丰富的经验和成果,并不断引入先进的设备和技术,为客户提供高水平的技术支持和服务。4.北京中科微电子有限公司失效分析实验室北京中科微电子有限公司是一家专业从事半导体封装测试与分析的公司。实验室配备有一批优秀的专业技术人员和一流的设备,能够为客户提供全面、高效的失效分析服务。5.惠州半导体失效分析中心惠州半导体失效分析中心是惠州市政府支持的创新创业平台,依托留学海归、国内外知名院校科研机构等优势资源,致力于半导体失效分析领域的研发和服务。6.中国电子科技集团公司第十四研究所该实验室成立于20世纪80年代,针对集成电路芯片的失效问题,建立了先进的实验室设备和完整的芯片失效分析技术流程。这些技术流程包括非常规样品处理、样品制备、分析测试和故障分析定位等。该实验室能够对各种类型的芯片进行失效分析,如DRAM、NOR FLASH、SRAM、Flip Chip等。7.中国电子科技集团公司第五十五研究所该实验室成立于20世纪90年代,主要研究领域是空间电子电路可靠性和失效分析。在芯片失效分析方面,该实验室研究了很多芯片失效的根本原因和解决办法。例如,该实验室率先提出了在高温下检测集成电路失效的方法,推出了系列失效分析和故障定位技术。8.中国航天科工集团有限公司第六十所该实验室成立于20世纪90年代初期,由中国第一位半导体芯片设计师胡启恒教授领导,主要研究集成电路的失效分析和检测。该实验室在失效分析方面的主要技术包括侵入式和非侵入式技术、信号分析、快速失效分析以及优化分析等。此外,该实验室还开创了集成电路失效分析的新技术领域。9.南京微米尺度材料分析与应用国家级实验室该实验室拥有完整的半导体芯片失效分析实验平台及技术团队,能够进行芯片性能评估、芯片分析、缺陷定位和失效机理研究等多方面的工作,可为企业提供完整的半导体芯片失效分析服务。10.北京微电子所半导体芯片失效分析实验室该实验室依托于北京微电子所,能够利用所拥有的半导体芯片分析技术和完善的实验平台,提供专业的半导体芯片失效分析服务,包括芯片失效原因分析、失效机理研究、失效模拟与验证等多方面的服务。11.武汉微纳电子制造国家工程研究中心半导体芯片失效分析实验室武汉微纳电子制造国家工程研究中心依托于华中科技大学,其半导体芯片失效分析实验室拥有全套高端的半导体芯片失效分析仪器,为企业提供完整的半导体芯片失效分析服务,涉及芯片失效原因分析、失效机理研究、失效模拟与验证等多方面的服务。12.上海微电子设备有限公司半导体芯片失效分析实验室该实验室作为上海微电子设备有限公司的技术支持,结合上海微电子设备有限公司的芯片检测与分析设备,可为企业提供完整的半导体芯片失效分析服务,包括芯片失效原因分析、失效机理研究、失效模拟与验证等多方面的服务。以上仅是部分中国半导体芯片失效分析实验室,随着技术的不断更新和进步,相信未来将会涌现更多实验室,并且实验室之间也将进行更多的协作与交流,加速半导体芯片失效分析技术的发展和普及。国内较为知名的半导体芯片失效分析实验室还有中芯国际、台积电、联芯科技等。这些实验室拥有一流的实验设备和技术人才,可以开展多种类型的半导体芯片失效分析工作,并为客户提供专业的技术支持和服务。此外,在国际上也有多家著名的半导体芯片失效分析实验室,如SiliconExpert、IEEE Components Partitioning and Analysis Center等。这些实验室不仅具备高水平的技术装备和技术人才,还通过与多家知名公司合作,积累了丰富的经验和数据资源。同时,这些实验室还开展了大量的研究工作,不断推动半导体芯片失效分析领域的发展。总之,半导体芯片失效分析实验室在提高半导体芯片可靠性方面起着至关重要的作用。希望通过本文的介绍,可以帮助大家了解半导体芯片失效分析实验室的相关情况,为半导体芯片失效分析工作提供参考和支持。[img]https://ng1.17img.cn/bbsfiles/images/2023/05/202305240713065889_2888_3233403_3.png[/img]

半导体芯片高低温测试机在运行的过程中,每个配件的性能都是很关键的,无锡冠亚的半导体芯片高低温测试机中真空泵一旦发生故障的话,就需要及时维修以及保养,这些都是不可少的。 半导体芯片高低温测试机真空泵完好标准是机体整洁,零部件完整齐全,质量符合要求。真空表、电流表等仪表齐全、灵敏、准确,并有定期检验标志。基础稳固可靠,地脚螺栓和各部螺栓连接紧固、齐整,丝扣外露长度符合规定。管线、阀门等安装合理,标志分明,符合要求。各零部件的安装间隙应达到规定要求。半导体芯片高低温测试机真空泵运行性能要求要注意半导体芯片高低温测试机的润滑良好,油质符合要求,实行“五定”,设备运转平稳无杂音,其振动和噪声不应超过有关规定,设备负荷运转时,温度、压力、流量、电流等参数应符合相关标准。 半导体芯片高低温测试机真空泵设备及环境要求需要注意泵体清洁,外表无尘灰、油垢。基础底座表面及周围无积水、废液及其他杂物等。阀门及管件接头等处不得有泄漏。填料密封处泄漏不超过规定。 半导体芯片高低温测试机真空泵日常维护需要注意半导体芯片高低温测试机周围环境应保持清洁、干燥,通风良好,检查冷却水路是否畅通,检查各润滑部位的润滑油是否符合规定。每班必须检查各部紧固螺栓,不得有松动现象,经常检查真空罐中的液位是否正常有效,并进行必要紧固。随时检查真空表、电流表的读数是否正常。随时注意观察半导体芯片高低温测试机运转有无异常声响或振动,必要时可报告有关部门进行状态。操作人员必须严格按《操作规程》进行操作,巡回检查发现问题必须及时处理。 半导体芯片高低温测试机中真空泵的故障解决也是影响整个半导体芯片高低温测试机运行的效果的,以及后期真空泵的保养也是很重要的,这些都是不可忽视的,望悉知。

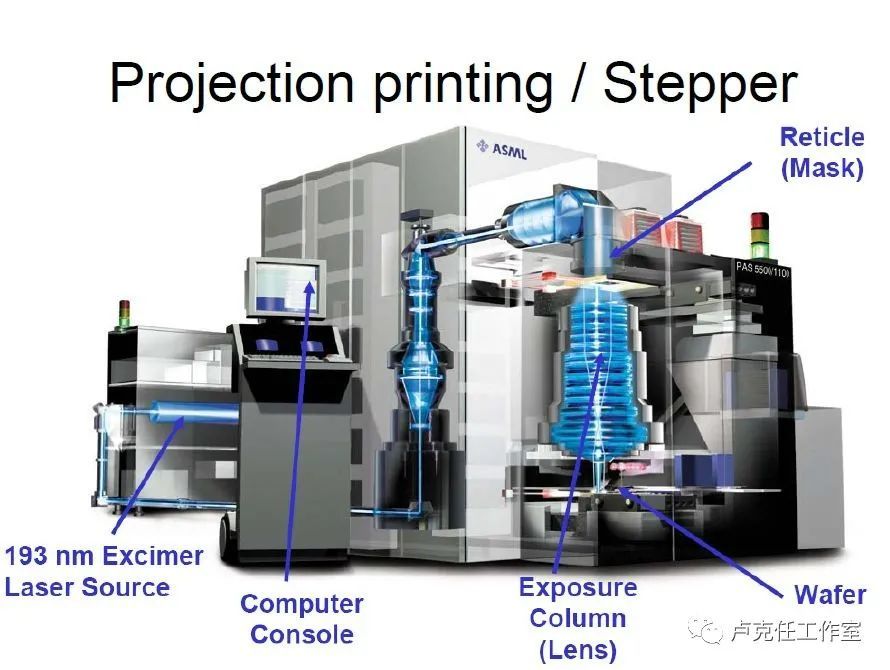

附件为半导体的生产流程图,简单介绍芯片的生产过程 石头-多晶硅-单晶硅(深蓝色)-切片(灰白色)-磨片-PN结扩散(深灰色)-上光胶-蚀刻-扩散-蒸发沉淀、覆盖氧化绝缘层(反复多次),颜色发生变化,每个步骤都不相同 单晶硅:硅晶圆材料,原子晶体结构,易碎,芯片厚度一般在0.4mm以下 芯片:由单晶硅经过多次化学反应,其中掺杂的离子很多,有多层扩散、覆盖、再腐蚀等过程组成,芯片生产过程中,要求材料的纯度极高,特别清洗过程的水都是纯水,空气粉尘等级10万级,掺杂的离子纯度要求很高,化学反应的气体一般是剧毒的。材料的纯度之高,如果有其它材料混入,芯片一般会报废,或者芯片的性能大打折扣(主要表现在漏电)! 芯片的扩散是立体的,不单单是一个层,在每道工艺的之后,芯片的颜色一般都会发生变化,不再是单纯的某一种颜色,不可分离的。 [color=#DC143C] 大家认为多种颜色的芯片混合检测,能接受吗?不能接受,又是如何处理的,谢谢回复![/color][img]http://www.instrument.com.cn/bbs/images/affix.gif[/img][url=http://www.instrument.com.cn/bbs/download.asp?ID=105862]半导体流程图示[/url]