推荐厂家

暂无

暂无

400-668-7609

400-668-7609

留言咨询

留言咨询

400-860-5168转5919

400-860-5168转5919

留言咨询

留言咨询

留言咨询

留言咨询

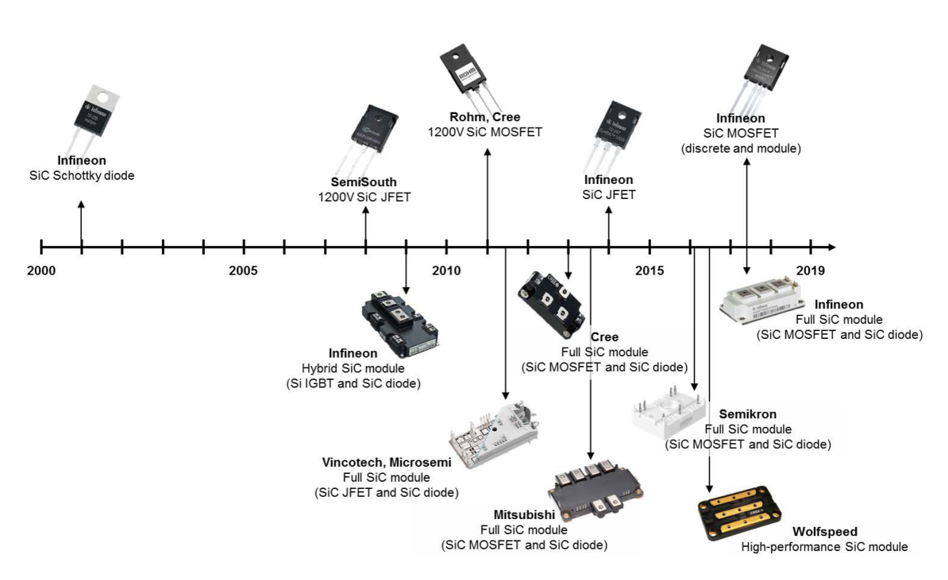

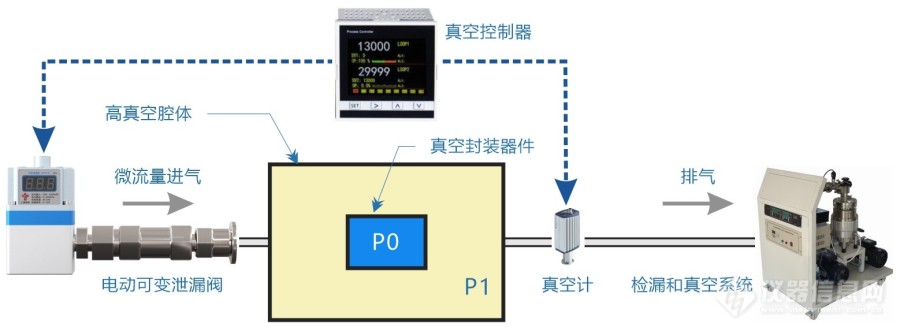

[size=16px][color=#339999][b]摘要:大量MEMS真空密封件具有小体积、高真空和无外接通气接口的特点,现有的各种检漏技术无法对其进行无损形式的漏率和内部真空度测量。基于压差法和高真空度恒定控制技术,本文提出了解决方案。方案的具体内容是将被测封装器件放置在一个比器件内部真空度更高的真空腔体内,采用电动可变泄漏阀和控制器自动调节微小进气流量进行高真空度控制,由此在被测器件内外建立恒定压差,通过测量此压差下的漏率可得到器件内部真空度。[/b][/color][/size][align=center][size=16px][color=#339999][b]=========================[/b][/color][/size][/align][size=18px][color=#339999][b]1. 问题的提出[/b][/color][/size][size=16px] 真空密封器件通常需要在特定的真空度下才能正常工作,即需要高真空度和长时间的真空保持度。例如杜瓦组件作为广泛使用的绝热容器在制冷、 红外探测以及超导中都有应用,而杜瓦的绝热效果与其夹层真空度直接相关。有机发光二极管对水蒸气和氧气含量特别敏感,工作时需要真空条件,含量超标的水蒸气和氧会严重影响其寿命和稳定性。高精度的MEMS惯性器件如MEMS陀螺仪、MEMS谐振式加速度计等需要工作在高真空环境中,其内部真空度的好坏决定其品质因数的大小。由此可见,为了保证真空密封器件的密封性能,需要对漏率和真空度的变化进行测试评价,但由于存在以下几方面的原因,使得这种评价技术成为目前迫切需要解决的难题:[/size][size=16px] (1)对于大多数真空密封器件而言,其几何尺寸一般很小,且不能配置真空度和漏率测量接口,这导致了很多现有真空测量领域的传感器和仪器都无法直接使用。[/size][size=16px] (2)对于个别真空封装器件,可通过在外部形成高压将示踪气体(如氦气)加载到真空封装器件内,然后再在外部抽真空条件下采用检漏仪测量真空封装器件的漏率。但这种方法往往会破坏真空封装器件内部的真空度,且不可逆转,可能会造成真空封装器件性能的降低。[/size][size=16px] (3)直接在真空密封器件内集成真空度传感器不失为一种有效手段,如集成如皮拉尼计和音叉石英晶振等,国内外的各种研究也曾在这方面做过努力,但由于所集成传感器自身特性(如结构形状、尺寸、真空度测量范围和精度等)以及所带来附加影响,使得这种技术仅勉强适用于个别真空密封器件,根本无法作为一种通用技术得以应用。[/size][size=16px] 为了解决目前真空封装器件存在的检漏问题,特别是实现对真空封装器件内部真空度的测量,本文基于压差法提出了一种间接测量的解决方案。[/size][size=18px][color=#339999][b]2. 解决方案[/b][/color][/size][size=16px] 对于内部具有一定真空度的真空封装器件,其漏率和内部真空度的测量将基于压差法。具体是即将被测真空封装器件放置在一个要比器件内部真空度更高的密闭腔体内,由此在封装器件内外形成压差。通过测量获得此压差下的漏率,然后再通过漏率计算出器件内部真空度。[/size][size=16px] 依据解决方案设计的真空封装器件漏率和真空度测量装置结构如图1所示。[/size][align=center][size=16px][color=#339999][b][img=真空密封器件漏率和真空度测试系统结构示意图,690,253]https://ng1.17img.cn/bbsfiles/images/2023/09/202309041023569886_4228_3221506_3.jpg!w690x253.jpg[/img][/b][/color][/size][/align][align=center][size=16px][color=#339999][b]图1 真空密封器件漏率和真空度测试系统结构示意图[/b][/color][/size][/align][size=16px] 依据检漏中的压差法原理,漏率的测量结果与压差(P1-P0)呈线性关系。因此,如图1所示,只要精确控制密闭腔体内的真空度P1,在测量得到漏率后,就可以计算出真空封装器件内部的真空度。由此可见,测试真空密封器件漏率和真空度需要解决以下两个关键问题:[/size][size=16px] (1)腔体真空度P1的精确控制:对于具有高真空(如P01E-03Pa)的封装器件,腔体真空度需要达到P11E-03Pa的更高真空度,以形成尽可能大的压差,这就要求对超高真空度能实现准确控制,控制精度越高则计算得到器件内部真空度的精度越高。[/size][size=16px] (2)漏率测量:漏率测量也是决定精度的关键因素,具体实施时可以采用各种高灵敏度的漏率测量方法,如氦质谱检漏仪。为了实现定量和高精度的漏率测量,也可以采用特殊设计的漏率测试系统,但这部分内容不在本文阐述的内容之内。[/size][size=16px] 本文的重点是介绍解决方案中的超高真空度精密控制技术。如图1所示,超高真空度的控制采用调节进气流量来实现,具体采用了VLV2023型号的电动可变泄漏阀,进气流量的调节范围是1E-8PaL/s~500PaL/s,调节信号为0~10V。超高真空度控制回路有真空计、真空控制器和电动可变泄漏阀组成,真空控制器采集真空计信号并与设定值进行比较后,输出PID控制信号对可变泄漏阀进行驱动来调节微小的进气流量,由此使腔体真空度快速恒定在设置值处。[/size][size=16px] 在超高真空控制中还面临另外一个问题是真空计输出信号的非线性,为此本文解决方案中采用了具有线性化处理功能的VPC2021系列真空压力控制器,通过在真空和电压的关系曲线中取八个数据点进行拟合,可很好的解决线性PID控制非线性信号的问题。[/size][size=18px][color=#339999][b]3. 总结[/b][/color][/size][size=16px] 综上所述,本解决方案很好的突破了真空密封件漏率和内部真空度测量难题,关键是实现了高真空度精密控制中的微小进气流量自动调节以及传感器非线性输出信号的PID控制器线性化处理。解决方案中的高真空度控制装置可广泛应用于任何真空系统,PID控制器线性化技术可广泛应用于各种非线性传感器测量控制场合。[/size][size=16px] 本解决方案对高真空微小压差下的漏率测试技术并未做详细的介绍,这部分内容将在后续研究报告中给出详细的测试系统描述。[/size][size=16px][/size][align=center][b][color=#339999]~~~~~~~~~~~~~~~~~~[/color][/b][/align]

力标精密设备有限公司产品广泛用于半导体封装测试,LED封装测试,摄像头模组测试,光通领域,电子器件,目前已成为一流测力设备制造商搜索复制

PCB封装实际就是把元器件、芯片等各种参数(如大小、长宽、焊盘的大小等)用图形的方式表现出来,这样才可以在画PCB图时进行调用。所以在PCB设计前,元件的选择就成了重中之重,否则在设计时总会遇到这样那样的问题,从而导致你花了大量时间设计出的PCB板从不能在实际上运用。今天请元坤智造的工程师为大家介绍一些在选择PCB元件时需要注意的地方。 这里主要是说了从PCB设计封装来解析选择元件的技巧。元件的封装包含很多信息,包含元件的尺寸,特别是引脚的相对位置关系,还有元件的焊盘类型。当然我们根据元件封装选择元件时还有一个要注意的地方是要考虑元件的外形尺寸。 引脚位置关系:主要是指我们需要将实际的元件的引脚和PCB元件的封装的尺寸对应起来。我们选择不同的元件,虽然功能相同,但是元件的封装很可能不一样。我们需要保证PCB焊盘尺寸位置正确才能保证元件能正确焊接。 焊盘的选择:这个是我们需要考虑的比较多的地方。 首先包括焊盘的类型。其类型包括两种,一是电镀通孔,一种是表贴类型。我们需要考虑的因素有器件成本、可用性、器件面积密度和功耗等因数。从制造角度看,表贴器件通常要比通孔器件便宜,而且一般可用性较高。对于我们一般设计来说,我们选择表贴元件,不仅方便手工焊接,而且有利于查错和调试过程中更好的连接焊盘和信号。 其次我们还应该注意焊盘的位置。因为不同的位置,就代表元件实际当中不同的位置。我们如果不合理安排焊盘的位置,很有可能就会出现一个区域元件过密,而另外一个区域元件很稀疏的情况,当然情况更糟糕的是由于焊盘位置过近,导致元件之间空隙过小而无法焊接,下面就是我失败的一个例子,我在一个光耦开关旁边开了通孔,但是由于它们的位置过近,导致光耦开关焊接上去以后,通孔无法再放置螺丝了。 另外一种情况就是我们要考虑焊盘如何焊接。在实际过程中我们常按一个特定的方向排列焊盘,焊接起来比较方便。 元件的外形尺寸:在实际应用当中,一些元件(如有极性电容)可能有高度净空限制,所以我们需要在元件选择过程中加以考虑。我们在最初开始设计时,可以先画一个基本的电路板外框形状,然后放置上一些计划要使用的大型或位置关键元件(如连接器)。这样,就能直观快速地看到(没有布线的)电路板虚拟透视图,并给出相对精确的电路板和元器件的相对定位和元件高度。这将有助于确保PCB经过装配后元件能合适地放进外包装(塑料制品、机箱、机框等)内。当然我们还可以从工具菜单中调用三维预览模式浏览整块电路板。 对于元件的选择,除了要依据设计要求外,还要选择正规厂家所生产的产品,这样才能保证实现你的设计目标。